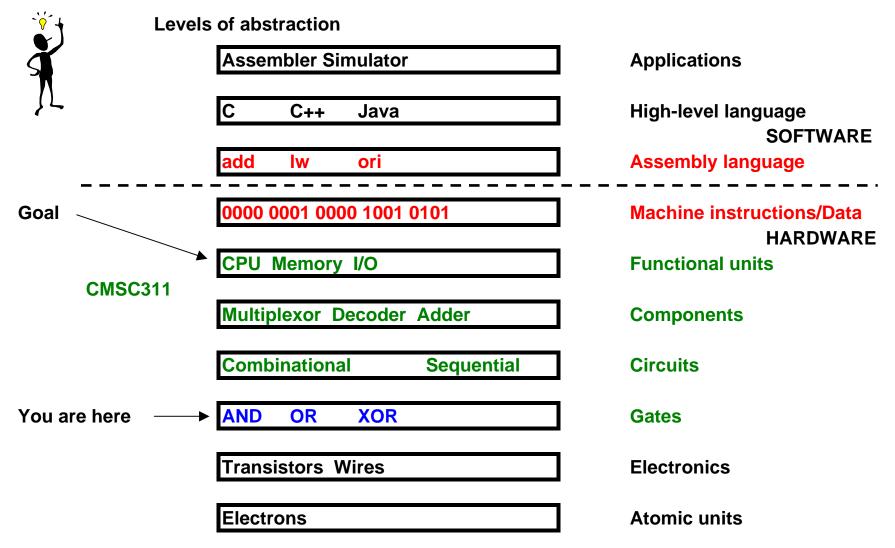

# **Computer organization**

## Gates

Gates: NOT Mr. Bill! Basic building blocks for circuits Implement boolean functions in hardware Computer engineering: how to build it physically Computer organization: how to design it logically Combinational circuits Output depends only on input

Sequential circuits

Output depends on input AND current state

|   |   | NOT |    | AND | OR    | XOR   | NOR      | NAND     | XNOR     |

|---|---|-----|----|-----|-------|-------|----------|----------|----------|

| a | b | ~a  | ~b | a&b | a   b | a ^ b | ~(a   b) | ~(a & b) | ~(a ^ b) |

| 0 | 0 | 1   | 1  | 0   | 0     | 0     | 1        | 1        | 1        |

| 0 | 1 | 1   | 0  | 0   | 1     | 1     | 0        | 1        | 0        |

| 1 | 0 | 0   | 1  | 0   | 1     | 1     | 0        | 1        | 0        |

| 1 | 1 | 0   | 0  | 1   | 1     | 0     | 0        | 0        | 1        |

# **Gates: truth tables**

How many possible boolean functions of 2 variables?

Depends on number of outputs

4 possible inputs --> 16 possible outputs of 1 bit each

# **Gates: truth tables**

|         | Unsigned<br>Binary |   |   |   |   |   | Function<br>Name | Gates |

|---------|--------------------|---|---|---|---|---|------------------|-------|

| Inputs  |                    | a | 0 | 0 | 1 | 1 |                  |       |

|         | _                  | b | 0 | 1 | 0 | 1 |                  |       |

| Outputs | 0                  |   | 0 | 0 | 0 | 0 | FALSE            |       |

|         | 1                  |   | 0 | 0 | 0 | 1 | AND              |       |

|         | 2                  |   | 0 | 0 | 1 | 0 | a & ~b           |       |

|         | 3                  |   | 0 | 0 | 1 | 1 | a                |       |

|         | 4                  |   | 0 | 1 | 0 | 0 | ~a & b           |       |

|         | 5                  |   | 0 | 1 | 0 | 1 | b                |       |

|         | 6                  |   | 0 | 1 | 1 | 0 | XOR              |       |

|         | 7                  |   | 0 | 1 | 1 | 1 | OR               |       |

|         | 8                  |   | 1 | 0 | 0 | 0 | NOR              |       |

|         | 9                  |   | 1 | 0 | 0 | 1 | XNOR             |       |

|         | 10                 |   | 1 | 0 | 1 | 0 | ~b               |       |

|         | 11                 |   | 1 | 0 | 1 | 1 | a   ~b           |       |

|         | 12                 |   | 1 | 1 | 0 | 0 | ~a               |       |

|         | 13                 |   | 1 | 1 | 0 | 1 | ~a   b           |       |

|         | 14                 |   | 1 | 1 | 1 | 0 | NAND             |       |

|         | 15                 |   | 1 | 1 | 1 | 1 | TRUE             |       |

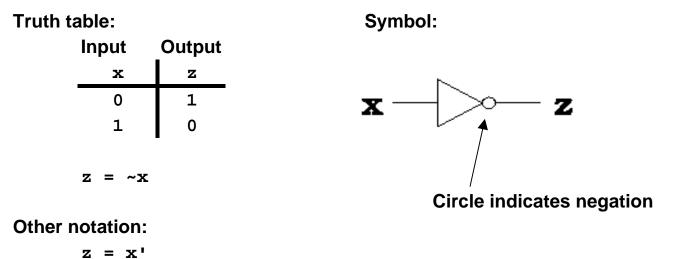

# **Gates: Inverter**

$z = \overline{x}$

$z = \backslash x$

# Inverter: implements NOT function Also known as "negation" or "complement" Input: 1 bit Output: 1 bit

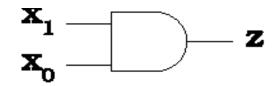

### **Gates: AND**

## AND gate: implements AND function Input: 2 bits Output: 1 bit

#### Truth table:

| Input                 | Output         |   |  |  |

|-----------------------|----------------|---|--|--|

| <b>x</b> <sub>0</sub> | $\mathbf{x}_1$ | Z |  |  |

| 0                     | 0              | 0 |  |  |

| 0                     | 1              | 0 |  |  |

| 1                     | 0              | 0 |  |  |

| 1                     | 1              | 1 |  |  |

Symbol:

$\mathbf{z} = \mathbf{x}_0 \& \mathbf{x}_1$

Other notation:

**Properties:**

$z = AND (x_0, x_1)$  symmetric: x \* y = y \* x  $z = x_0 * x_1$  associative: (x \* y) \* z = x \* (y \* z) $z = x_0 x_1$

n inputs:

$AND_n$  (x<sub>0</sub>, x<sub>1</sub>, . . . , x<sub>n</sub>) = x<sub>0</sub> \* x<sub>1</sub> \* . . . x<sub>n</sub>

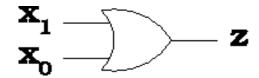

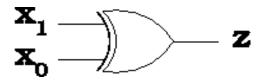

# Gates: OR

# OR gate: implements OR function Input: 2 bits Output: 1 bit

#### Truth table:

| Input            | Output         |   |  |  |

|------------------|----------------|---|--|--|

| $\mathbf{x}_{0}$ | $\mathbf{x}_1$ | Z |  |  |

| 0                | 0              | 0 |  |  |

| 0                | 1              | 1 |  |  |

| 1                | 0              | 1 |  |  |

| 1                | 1              | 1 |  |  |

Symbol:

| $\mathbf{z} = \mathbf{x}_0 \mid \mathbf{x}_1$ |                    |                                                     |

|-----------------------------------------------|--------------------|-----------------------------------------------------|

| Other notation:                               | <b>Properties:</b> |                                                     |

| $z = OR (x_0, x_1)$                           | symmetric:         | $\mathbf{x} + \mathbf{y} = \mathbf{y} + \mathbf{x}$ |

| $z = x_0 + x_1$                               | associative:       | (x + y) + z = x + (y + z)                           |

n inputs:

$OR_n$  (x<sub>0</sub>, x<sub>1</sub>, . . . , x<sub>n</sub>) = x<sub>0</sub> + x<sub>1</sub> + . . . x<sub>n</sub>

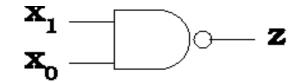

### **Gates: NAND**

## NAND gate: implements NAND (negated AND) function Input: 2 bits Output: 1 bit

#### Truth table:

Symbol:

| Input                 | Output         |   |  |  |

|-----------------------|----------------|---|--|--|

| <b>x</b> <sub>0</sub> | $\mathbf{x}_1$ | Z |  |  |

| 0                     | 0              | 1 |  |  |

| 0                     | 1              | 1 |  |  |

| 1                     | 0              | 1 |  |  |

| 1                     | 1              | 0 |  |  |

$z = x_0$  NAND  $x_1$

**Properties:**

symmetric: x NAND y = y NAND xnot associative

n inputs:

$NAND_n$  (x<sub>0</sub>, x<sub>1</sub>, . . . , x<sub>n</sub>) = NOT (x<sub>0</sub> \* x<sub>1</sub> \* . . . x<sub>n</sub>)

## **Gates: NOR**

## NOR gate: implements NOR (negated OR) function Input: 2 bits Output: 1 bit

#### Truth table:

Symbol:

| Input            | Output         |   |  |  |

|------------------|----------------|---|--|--|

| $\mathbf{x}_{0}$ | $\mathbf{x}_1$ | Z |  |  |

| 0                | 0              | 1 |  |  |

| 0                | 1              | 0 |  |  |

| 1                | 0              | 0 |  |  |

| 1                | 1              | 0 |  |  |

$z = x_0$  NOR  $x_1$

**Properties:**

symmetric: x NOR y = y NOR x not associative

n inputs:

$NOR_n$  ( $x_0$ ,  $x_1$ , . . . ,  $x_n$ ) = NOT ( $x_0$  +  $x_1$  + . . .  $x_n$ )

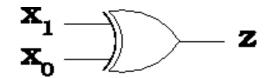

# **Gates: XOR**

# XOR gate: implements exclusive-OR function Input: 2 bits Output: 1 bit

#### Truth table:

Symbol:

| Input            | Output         |   |  |  |  |

|------------------|----------------|---|--|--|--|

| $\mathbf{x}_{0}$ | $\mathbf{x}_1$ | Z |  |  |  |

| 0                | 0              | 0 |  |  |  |

| 0                | 1              | 1 |  |  |  |

| 1                | 0              | 1 |  |  |  |

| 1                | 1              | 0 |  |  |  |

$$\mathbf{z} = \mathbf{x}_0 \wedge \mathbf{x}_1$$

**Properties:**

symmetric:  $x \land y = y \land x$ associative:  $(x \land y) \land z = x \land (y \land z)$

n inputs:

$$XOR_n$$

( $x_0$ ,  $x_1$ , . . . ,  $x_n$ ) =  $x_0 \land x_1 \land . . . x_n$

# **Gates: XOR properties**

Truth table:

|                | Output      |

|----------------|-------------|

| $\mathbf{x}_1$ | Z           |

| 0              | 0           |

| 1              | 1           |

| 0              | 1           |

| 1              | 0           |

|                | 0<br>1<br>0 |

Symbol:

XOR can be expressed in terms of AND, OR, NOT:

x XOR y == (x AND (NOT y)) OR ((NOT x) AND y)

(If x is true, y must be false, and vice versa.)

$\mathbf{x}_{_0} ~ ^{ } ~ \mathbf{x}_{_1} ~ ^{ } ~ .$  . .  $\mathbf{x}_{_n} ~$  is true if the number of true values is odd,

and false if the number of true values is even. Why?

$\mathbf{x}_0 \wedge \mathbf{x}_1 \wedge \ldots \mathbf{x}_n == (\mathbf{x}_0 + \mathbf{x}_1 + \ldots \mathbf{x}_n) \% 2$

XOR is the same as the sum modulo 2

| $\mathbf{x} \wedge 0 = \mathbf{x}$ | XORing with 0 gives you back the same number (identity) |

|------------------------------------|---------------------------------------------------------|

| $x \wedge 1 = x$                   | XORing with 1 gives you the complement                  |

| $\mathbf{x} \wedge \mathbf{x} = 0$ | XORing a number with itself gives 0                     |

## **Gates: XOR properties**

More XOR tricks (amaze your friends!): Classic swap problem (early CMSC 106)

> temp = x; x = y; y = temp;

Using XOR:

x = x ^ y ; y = x ^ y ; x = x ^ y ;

Let  $x_0$  be the original value of x,  $y_0$  be the original value of y:

```

\mathbf{x} = \mathbf{x} \wedge \mathbf{y} = \mathbf{x}0 \wedge \mathbf{y}0

y = x \wedge y = (x0 \wedge y0) \wedge y0 Substitute for x

= x0 ^{(y0 ^{y0})}

Associative property

= x0 ^{0}

x^{x} = 0

= \mathbf{x}\mathbf{0}

Identity

Substitute for x and y

x = x^{y} = (x0^{y} + y0)^{y} = x0^{y}

Associative, symmetric properties

= (x0 ^ x0) ^ y0

= 0 ^{y} 0

x^{x} = 0

Identity

= y0

```

What other operator is a less-safe way of doing this?

### **Gates: XNOR**

XNOR gate: implements XNOR (negated exclusive-OR) function Input: 2 bits Output: 1 bit

#### Truth table:

Symbol:

| Input            |                | Output |                |

|------------------|----------------|--------|----------------|

| $\mathbf{x}_{0}$ | $\mathbf{x}_1$ | Z      |                |

| 0                | 0              | 1      |                |

| 0                | 1              | 0      | <b>x</b> // >> |

| 1                | 0              | 0      |                |

| 1                | 1              | 1      |                |

$z = x_0 XNOR x_1 = \sim (x_0 \land x_1)$

**Properties:**

symmetric: x XNOR y = y XNOR x

associative: (x XNOR y) XNOR z = x XNOR (y XNOR z)

n inputs:

$XNOR_n$  ( $x_0$ ,  $x_1$ , . . . ,  $x_n$ ) =  $x_0$  XNOR  $x_1$  XNOR . . .  $x_n$

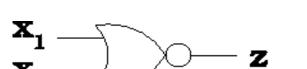

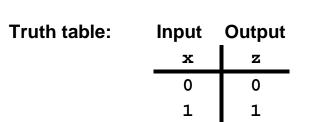

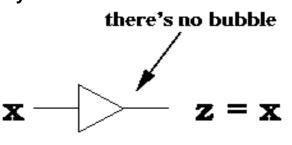

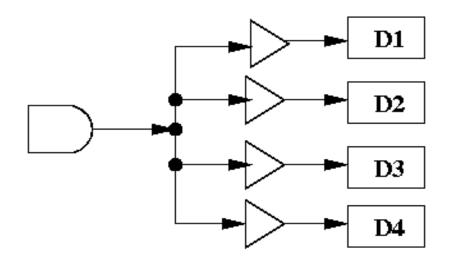

### **Gates: Buffer**

Buffer: implements equality function Input: 1 bit Output: 1 bit

Symbol:

This doesn't look very interesting at all!

There is a practical reason for it, however:

Circuits use electrical signals: 0 and 1 are represented by voltage.

If current is too low, it's hard to measure voltage accurately.

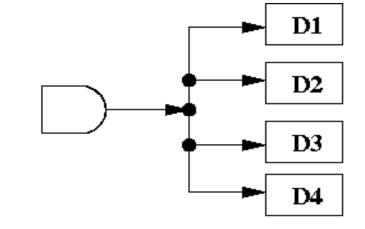

"Fan out" (number of devices) reduces

amount of current.

If the current from the AND gate is

distributed equally, then each device gets 1/4 the current.

A buffer can be used to "boost" the current back to the right level:

The buffer (like all other gates) is an active device; it requires power input to maintain current and voltage.

That's all EE stuff, and we're programmers. Why should we care about that?

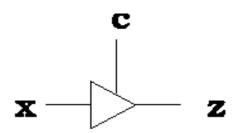

# **Gates: Tri-State Buffer**

A tri-state buffer acts like a valve: controls flow of current.

Input: 2 bits

Output: 1 bit

Truth table:

| Input |   | Output |   |            |

|-------|---|--------|---|------------|

| С     | x | Z      |   |            |

| 0     | 0 | Z      | J | no current |

| 0     | 1 | Ζ      | ſ |            |

| 1     | 0 | 0      | - |            |

| 1     | 1 | 1      |   |            |

| simplified: | active-high |        |

|-------------|-------------|--------|

|             | Input       | Output |

|             | С           | z      |

|             | 0           | Z      |

|             | 1           | x      |

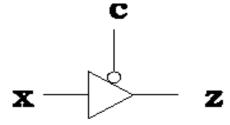

active-low

Output

z

$\mathbf{x}$

Ζ

Input

C

0

1

When c = 1, the output is equal to x, otherwise there is no output. Active-low: Output is x when c = 0.

tri-state buffer with active high control

tri-state buffer with active low control

## **Circuits**

Gates may be connected to build circuits

Valid combinational circuits

The output of a gate may only be attached to the input of another gate. Think of this as a directed edge from output to input. There must be no cycles in the circuit (directed graph). Although the output of a gate may be attached to more than one input, an input may not have two different outputs attached to it (This would create conflicting input signals.) Each input of a gate must come from either the output of another gate or a source. Source: something which generates either a constant 0 or 1. Gate delay Output takes some small amount of time before it changes. Information can travel at most, at the speed of light.

Gate delay limits how fast the inputs can change and

the output can still have meaningful values.

This document was created with Win2PDF available at <a href="http://www.daneprairie.com">http://www.daneprairie.com</a>. The unregistered version of Win2PDF is for evaluation or non-commercial use only.