|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

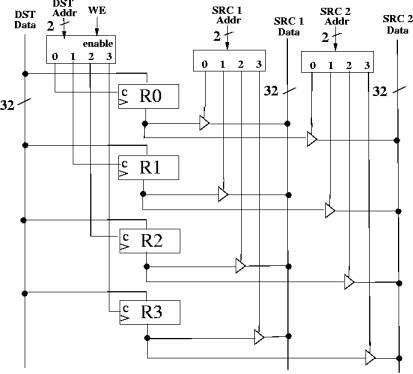

Register file:

implementing |

|

|

|

|

|

|

|

Destination register |

|

|

|

DST Addr: destination

register address |

|

|

DST Data: data to store

in destination register |

|

|

Write Enable (WE)

indicates when to write the destination register |

|

|

|

|

WE = 1: write to the

register specified by DST Addr |

|

|

|

|

WE = 0: don't do anything |

|

|

|

|

2 bits of DST Addr tell

which register to write |

|

|

|

|

Want control input c of

destination register to be 1 when WE = 1, |

|

|

|

|

all other registers must

have c = 0 |

|

|

|

|

What device to use? |

|

|

|

|

2-4 decoder with enable

or 1-4 DeMUX |

|

|

|

|

choose decoder |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

parts list: |

|

|

|

|

|

four parallel load

registers |

|

|

|

|

two 2-4 decoders |

|

|

|

|

one 2-4 decoder with

enable |

|

|

|

|

eight tri-state buffers |

|

|

|

|

three

buses |

|

|

|

|

anything else? |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|