| Register access: R-type | ||||||||||||||

|

||||||||||||||

| Components | ||||||||||||||

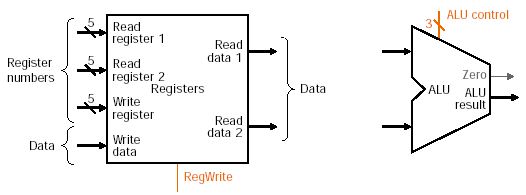

| Register file: 32 registers | Fig. 5.6 | |||||||||||||

| Inputs | ||||||||||||||

| 2 read register numbers (5 bits each) | ||||||||||||||

| 1 write register number (5 bits) | ||||||||||||||

| write data (32 bits) | ||||||||||||||

| Outputs: 2 read data values (32 bits each) | ||||||||||||||

| Control: RegWrite determines whether to write data to target register (1 bit) | ||||||||||||||

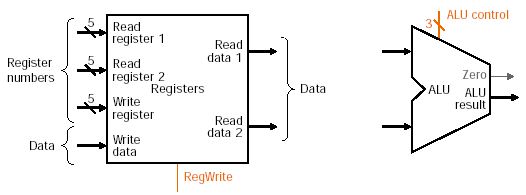

| ALU: performs arithmetic/logical operations | ||||||||||||||

| Inputs: 2 data values (32 bits each) | ||||||||||||||

| Outputs | ||||||||||||||

| Result of operation (32 bits) | ||||||||||||||

| Zero: result is equal to 0 (1 bit) | ||||||||||||||

| Control: ALU control selects operation (3 bits) | ||||||||||||||