|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

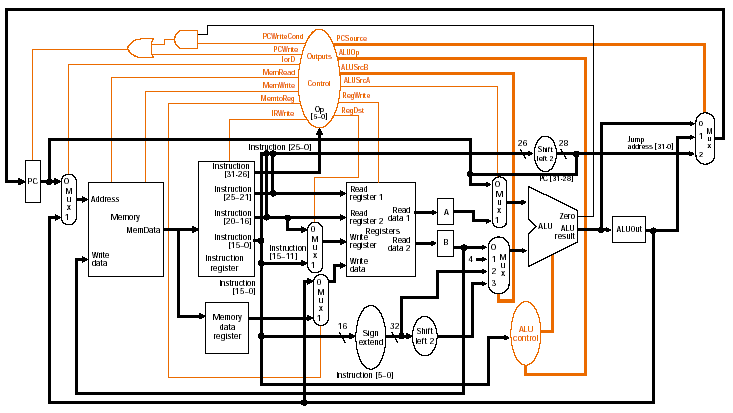

Multi-cycle datapath:

decode |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2. Instruction decode and

register fetch |

|

Fig. 5.33 |

|

|

|

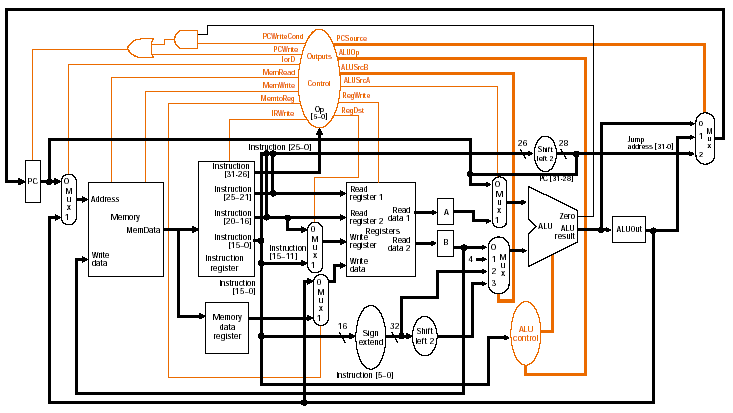

What do we know about

the type of instruction so far? Nothing! |

|

|

|

|

So,

we can only perform operations which apply to all instructions, |

|

|

|

|

|

or do not conflict with

the actual instruction |

|

|

|

|

What can we do at this

point? |

|

|

|

|

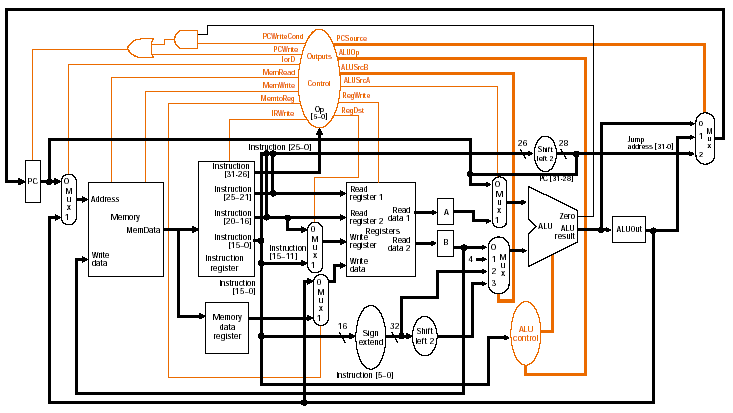

Read the registers from

the register file into A and B |

|

|

|

|

Compute branch address

using ALU and save in ALUOut |

|

|

|

|

But, what if the

instruction doesn't use 2 registers, or it isn't a branch? |

|

|

|

|

No

problem; we can simply use what we need once we know what |

|

|

|

|

|

kind of instruction we

have |

|

|

|

|

|

|

This is why having a

regular instruction pattern is a good idea. |

|

|

|

|

Is this inefficient? |

|

|

|

|

|

|

|

It does use up a little

more power and generate some heat, but it doesn't cost any TIME |

|

|

In fact, it means that

the entire instruction can be executed in fewer clock cycles |

|

|

|

Operation: |

|

|

|

|

|

A = Reg[IR[25-21]]; |

|

|

|

|

B = Reg[IR[20-16]]; |

|

|

|

|

ALUOut = PC + sign_extend

(IR[15-0]) << 2; |

|

|

|

|

What are the control

signals to determine whether to write registers A and B? |

|

|

|

There aren't any! We can read the register file and store A

and B on EVERY clock cycle. |

|

Branch address

computation: |

|

|

|

|

|

ALUSrcA = 0: PC to ALU |

|

|

|

|

|

ALUSrcB = 11:

sign-extended/shifted immediate to ALU |

|

|

|

|

|

ALUOp = 00: add |

|

|

|

|

These operations occur in

parallel. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|