|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Cache: fully-associative |

|

|

|

|

|

|

|

More flexible cache

management |

|

|

|

|

fully-associative |

|

|

|

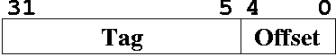

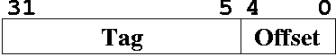

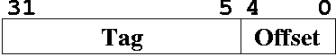

Assume cache consists of

27 = 128 slots, with 25 = 32 bytes per cache line |

|

|

|

Address A31-0 consists of tag bits A31-5 and offset A4-0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

If data not in the cache,

pick a slot |

|

|

|

|

Fully-associative cache:

may go in any slot |

|

|

|

|

Pick one with V = 0 |

|

|

|

|

|

|

If none, evict a slot

using replacement policy (LRU, FIFO, etc.) |

|

|

|

How do we know if a cache

line is in the cache? |

|

|

|

|

|

Must search every slot,

but hardware can search in parallel, unlike software |

|

|

|

Compare the address tag

bits with the tags of each slot in the cache |

|

|

|

|

Can be done using a

comparator (combinational circuit using XNOR gates) |

|

|

Must also have valid bit

V = 1 |

|

|

|

Complexity of hardware

to manage fully-associative cache slows down the speed |

|

|

|

of the cache, so it is

not generally used |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|