# K-maps and Sequential Circuits

250H

• Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Maurice Karnaugh developed the Karnaugh Map at Bell Labs in 1953

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Maurice Karnaugh developed the Karnaugh Map at Bell Labs in 1953

- K-maps come from venn diagrams

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Maurice Karnaugh developed the Karnaugh Map at Bell Labs in 1953

- K-maps come from venn diagrams

- Most people will use K-maps instead of boolean algebra when simplifying

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Maurice Karnaugh developed the Karnaugh Map at Bell Labs in 1953

- K-maps come from venn diagrams

- Most people will use K-maps instead of boolean algebra when simplifying

- K-maps do NOT always give the smallest circuit but they often do

- Previously in recitation, we looked at simplifying boolean expressions using algebraic manipulation

- Karnaugh Maps also simplify expressions in order to reduce the number of gates and inputs

- Maurice Karnaugh developed the Karnaugh Map at Bell Labs in 1953

- K-maps come from venn diagrams

- Most people will use K-maps instead of boolean algebra when simplifying

- K-maps do NOT always give the smallest circuit but they often do

- The problem of getting the BEST circuit is thought to be hard

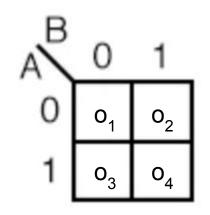

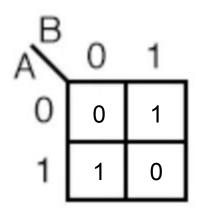

## K-maps for 2 Variables

• The outputs of a truth table correspond with a Karnaugh map entries

| A | В | Output         |

|---|---|----------------|

| 0 | 0 | 0 <sub>1</sub> |

| 0 | 1 | 0 <sub>2</sub> |

| 1 | 0 | 0 <sub>3</sub> |

| 1 | 1 | 0 <sub>4</sub> |

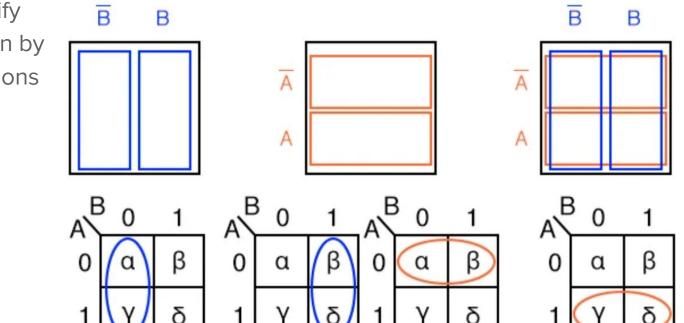

## K-maps for 2 Variables

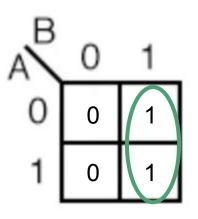

We can simplify the expression by using the regions shown here

- Without simplifying we can see that the output would be:

- $\circ \overline{AB} + AB$

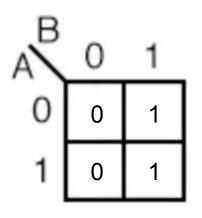

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

- Without simplifying we can see that the output would be:

- $\circ \overline{AB} + AB$

- We first translate the table to our k-map

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

- Without simplifying we can see that the output would be:

- $\circ \overline{AB} + AB$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

• Without simplifying we can see that the output would be:

$\circ \overline{AB} + AB$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

- Since we see that the 1's have a B in common

$\circ \ AB + AB \equiv B$

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 1      |

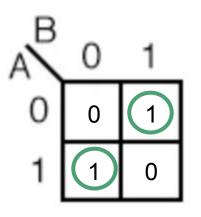

• Without simplifying we can see that the output would be:

$$\circ \ \overline{A}B + A\overline{B} + AB$$

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

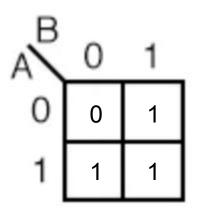

• Without simplifying we can see that the output would be:

$^{\circ} \overline{A}B + A\overline{B} + AB$

• We first translate the table to our k-map

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

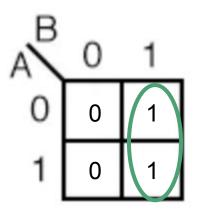

• Without simplifying we can see that the output would be:

$\circ \ \overline{A}B + A\overline{B} + AB$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

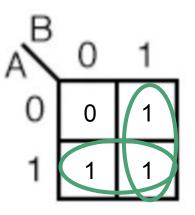

• Without simplifying we can see that the output would be:

$^{\circ} \overline{A}B + A\overline{B} + AB$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

- Since we see that the 1's have a B and A in common

$\circ \ \overline{A}B + A\overline{B} + AB \equiv A + B$

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 1      |

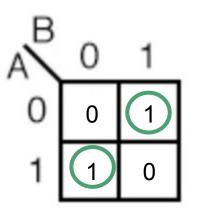

- Without simplifying we can see that the output would be:

- $\circ \ \overline{A}B + A\overline{B}$

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

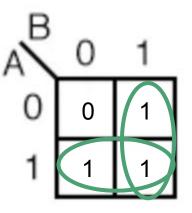

- Without simplifying we can see that the output would be:

- $\circ \ \overline{A}B + A\overline{B}$

- We first translate the table to our k-map

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

- Without simplifying we can see that the output would be:

- $\circ \ \overline{A}B + A\overline{B}$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

| A | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

• Without simplifying we can see that the output would be:

$\circ \overline{A}B + A\overline{B}$

- We first translate the table to our k-map

- We now want to look at the relationships of the 1's

- Since we see that we have nothing in common the simplest we can make this statement is  $\circ \overline{AB} + A\overline{B}$

| А | В | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

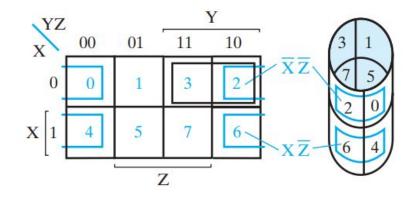

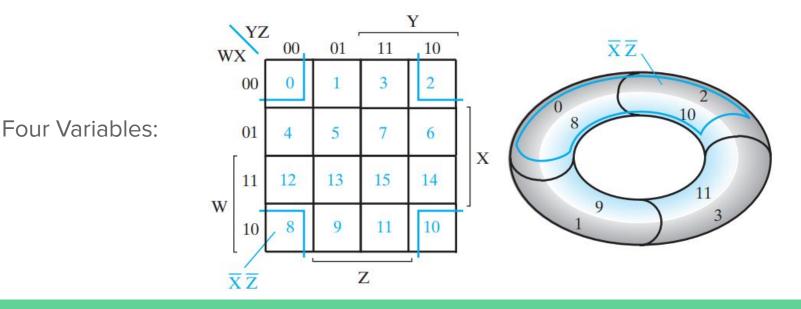

• Similarly we can extend this concept to more variables

- Similarly we can extend this concept to more variables

- When we have more variables we have to "fold" the map in order to see the relationships

- Similarly we can extend this concept to more variables

- When we have more variables we have to "fold" the map in order to see the relationships

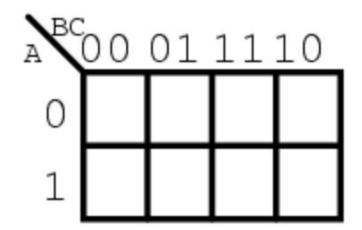

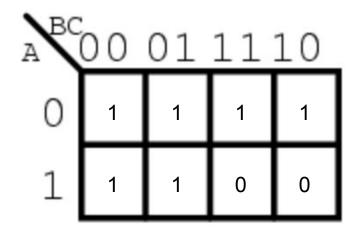

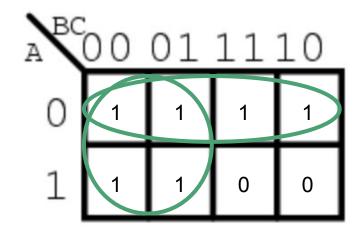

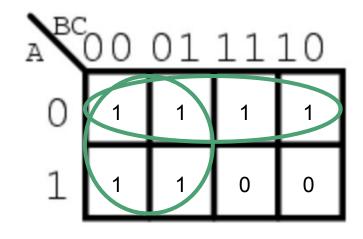

Three Variables:

- Similarly we can extend this concept to more variables

- When we have more variables we have to "fold" the map in order to see the relationships

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 1      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 0      |

Output:  $\overline{A} + \overline{B}$

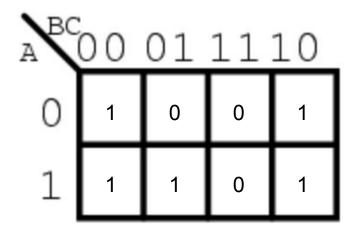

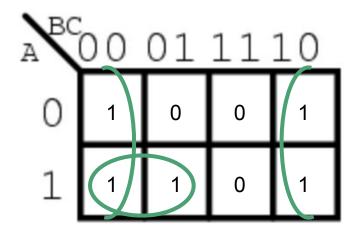

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

| А | В | С | Output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 1      |

| 0 | 1 | 1 | 0      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 1      |

| 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 0      |

Output:  $A\overline{B} + \overline{C}$

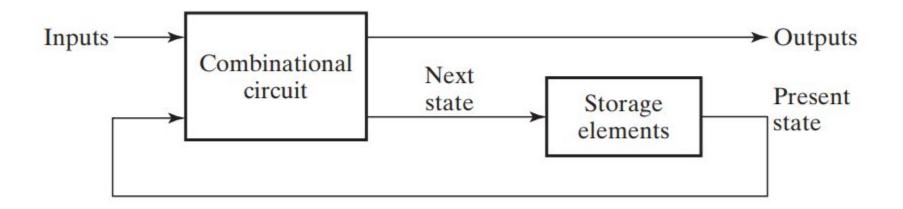

## **Sequential Circuits**

• The digital circuits we looked at previously have been combinational

## **Sequential Circuits**

- The digital circuits we looked at previously have been combinational

- Digital systems include a combinational circuit and storage elements

### **Sequential Circuits**

- The digital circuits we looked at previously have been combinational

- Digital systems include a combinational circuit and storage elements

- These storage elements are described as sequential circuits

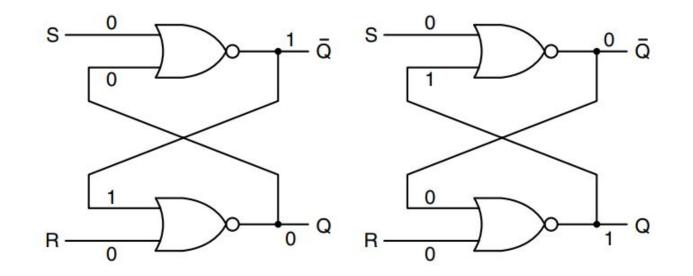

• To create a 1-bit memory, we need a circuit to remember a previous input value

- To create a 1-bit memory, we need a circuit to remember a previous input value

- We can construct this with two NOR gates

- To create a 1-bit memory, we need a circuit to remember a previous input value

- We can construct this with two NOR gates

- Two inputs

- $\circ$  S: Setting the Latch

- R: Resetting the latch

- Two inputs

- S: Setting the Latch

- R: Resetting the latch

- The outputs of the latch are not uniquely determined by the current inputs

- Two inputs

- S: Setting the Latch

- R: Resetting the latch

- The outputs of the latch are not uniquely determined by the current inputs

- When S is set to 1 momentarily, the latch ends up in state Q = 1, regardless of what state it was previously in

- Two inputs

- S: Setting the Latch

- R: Resetting the latch

- The outputs of the latch are not uniquely determined by the current inputs

- When S is set to 1 momentarily, the latch ends up in state Q = 1, regardless of what state it was previously in

- Setting R to 1 momentarily forces the latch to state Q = 0

- Two inputs

- S: Setting the Latch

- R: Resetting the latch

- The outputs of the latch are not uniquely determined by the current inputs

- When S is set to 1 momentarily, the latch ends up in state Q = 1, regardless of what state it was previously in

- Setting R to 1 momentarily forces the latch to state Q = 0

- The circuit "remembers" whether S or R was last on

- Two inputs

- S: Setting the Latch

- R: Resetting the latch

- The outputs of the latch are not uniquely determined by the current inputs

- When S is set to 1 momentarily, the latch ends up in state Q = 1, regardless of what state it was previously in

- Setting R to 1 momentarily forces the latch to state Q = 0

- The circuit "remembers" whether S or R was last on

- Using this property, we can build computer memories

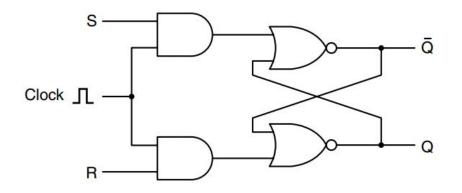

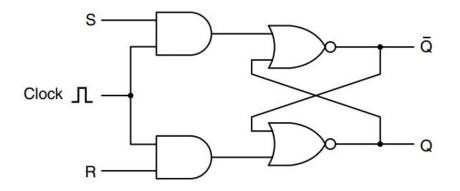

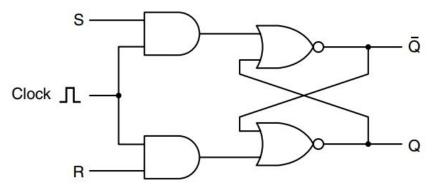

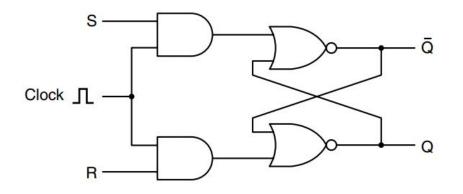

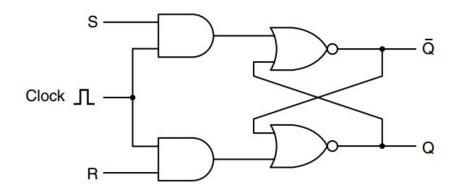

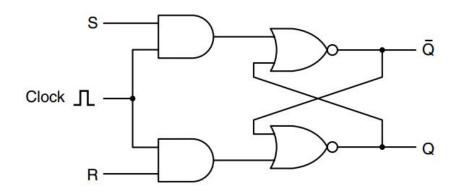

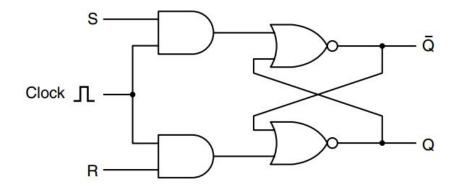

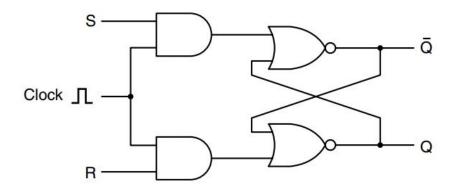

• We might need to prevent the latch from changing state except at certain specified times

- We might need to prevent the latch from changing state except at certain specified times

- We can modify the SR Latch slightly to get a clocked SR latch

- We might need to prevent the latch from changing state except at certain specified times

- We can modify the SR Latch slightly to get a clocked SR latch

- We might need to prevent the latch from changing state except at certain specified times

- We can modify the SR Latch slightly to get a clocked SR latch

- The circuit has an additional input for the clock and is normally set to 0

- We might need to prevent the latch from changing state except at certain specified times

- We can modify the SR Latch slightly to get a clocked SR latch

- The circuit has an additional input for the clock and is normally set to 0

- With the clock 0, both AND gates output 0, independent of S and R, and the latch does not change state

- With the clock 0, both AND gates output 0, independent of S and R, and the latch does not change state

- When the clock is 1, the effect of the AND gates vanishes and the latch relies on S and R

• What happens when S and R both equal 1?

- What happens when S and R both equal 1?

- The circuit becomes nondeterministic when both R and S finally return to 0

- What happens when S and R both equal 1?

- The circuit becomes nondeterministic when both R and S finally return to 0

- The only consistent state for S = R = 1 is  $Q = \overline{Q} = 0$ , but as soon as both inputs return to 0, the latch must jump to one of its two stable states

- What happens when S and R both equal 1?

- The circuit becomes nondeterministic when both R and S finally return to 0

- The only consistent state for S = R = 1 is  $Q = \overline{Q} = 0$ , but as soon as both inputs return to 0, the latch must jump to one of its two stable states

- The latch will jump to one of its stable states at random

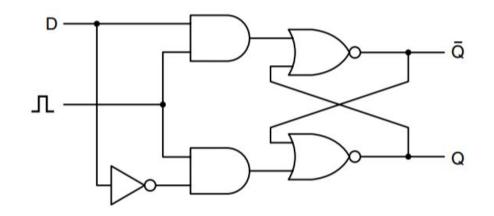

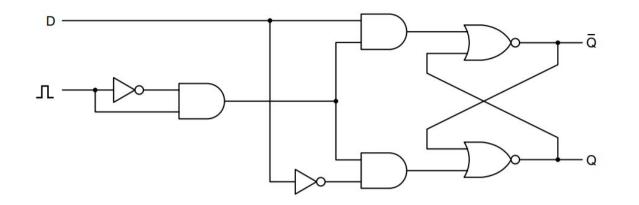

- We resolve this issue by preventing it from ever happening

- We create a circuit that only has one input: D

- Because the input to the lower AND gate is always the complement of the input to the upper one, the problem of both inputs being 1 never arises.

• Sometimes we need to sample the value on a certain line at a particular instant and store it

- Sometimes we need to sample the value on a certain line at a particular instant and store it

- The state transition during the clock transition from 0 to 1 or from 1 to 0 instead of when the clock is 1

- Sometimes we need to sample the value on a certain line at a particular instant and store it

- The state transition during the clock transition from 0 to 1 or from 1 to 0 instead of when the clock is 1

- This is called a Flip-Flop

- Sometimes we need to sample the value on a certain line at a particular instant and store it

- The state transition during the clock transition from 0 to 1 or from 1 to 0 instead of when the clock is 1

- This is called a Flip-Flop

• Flip-flops can be combined in groups to create registers, which hold data types larger than 1 bit in length

- Flip-flops can be combined in groups to create registers, which hold data types larger than 1 bit in length

- Eight flip-flops can be put together to form an 8-bit storage register

- Flip-flops can be combined in groups to create registers, which hold data types larger than 1 bit in length

- Eight flip-flops can be put together to form an 8-bit storage register

- The register accepts an 8-bit input value when the clock transitions

- Flip-flops can be combined in groups to create registers, which hold data types larger than 1 bit in length

- Eight flip-flops can be put together to form an 8-bit storage register

- The register accepts an 8-bit input value when the clock transitions

- To implement a register, all the clock lines are connected to the same input signal

- Flip-flops can be combined in groups to create registers, which hold data types larger than 1 bit in length

- Eight flip-flops can be put together to form an 8-bit storage register

- The register accepts an 8-bit input value when the clock transitions

- To implement a register, all the clock lines are connected to the same input signal

- Each register will accept the new 8-bit data value on the input bus