## START

# RECORDING

### Circuits

CMSC250

#### Circuits

- We can build circuits for addition, multiplication, division, bit shifting...

- Every logical operation we have learned (~,∧,∨) maps straightforwardly to a tiny piece of hardware called a *logical gate*.

- These gates connect to each other to make arbitrarily complicated circuits!

#### From a truth table to a formula

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### From a truth table to a formula

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

• Let us focus entirely on the rows that output 1!

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 1<sup>st</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

• Write a formula that is '1' only on inputs p =0, q = 0, r = 0.

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 1<sup>st</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

• Write a simple formula that is '1' only on inputs p =0, q = 0, r = 0.

$\sim p \land \sim q \land \sim r$

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 4<sup>th</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 0 | 1 | 1 | 1      |

Same deal

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 4<sup>th</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 0 | 1 | 1 | 1      |

• Same deal

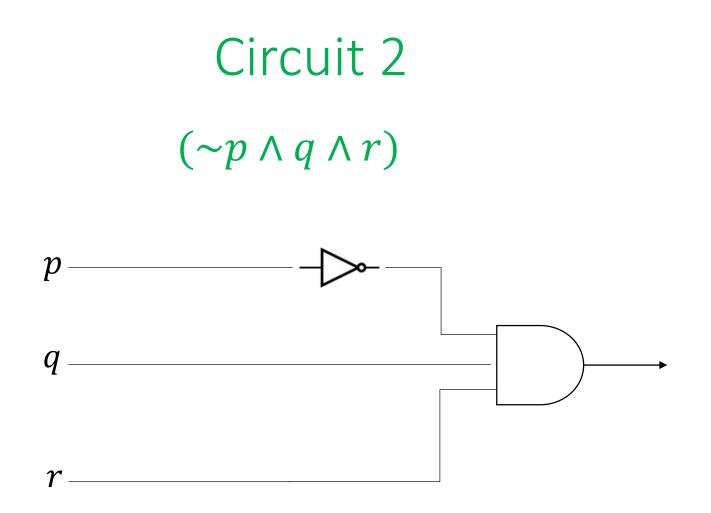

$\sim p \land q \land r$

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 5<sup>th</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 1 | 0 | 0 | 1      |

$p \wedge \sim q \wedge \sim r$

| р | q | r | output |

|---|---|---|--------|

| 0 | 0 | 0 | 1      |

| 0 | 0 | 1 | 0      |

| 0 | 1 | 0 | 0      |

| 0 | 1 | 1 | 1      |

| 1 | 0 | 0 | 1      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

#### Focusing on the 8<sup>th</sup> row...

| р | q | r | output |

|---|---|---|--------|

| 1 | 1 | 1 | 1      |

$p \land q \land r$

#### How do we combine those simple formulae?

$\sim p \land \sim q \land \sim r$

${\sim}p \wedge q \wedge r$

$p \wedge \sim q \wedge \sim r$

$p \land q \land r$

#### How do we combine those simple formulae?

| $(\sim p \land \sim q \land \sim r) \lor$ | р | q | r | output |

|-------------------------------------------|---|---|---|--------|

|                                           | 0 | 0 | 0 | 1      |

|                                           | 0 | 0 | 1 | 0      |

| $(\sim p \land q \land r) \lor$           | 0 | 1 | 0 | 0      |

|                                           | 0 | 1 | 1 | 1      |

|                                           | 1 | 0 | 0 | 1      |

| $(p \land \sim q \land \sim r) \lor$      | 1 | 0 | 1 | 0      |

|                                           | 1 | 1 | 0 | 0      |

| $(p \land q \land r)$                     | 1 | 1 | 1 | 1      |

| $(P \land q \land r)$                     |   |   | 5 |        |

• Outputs 1 if and only if the truth table outputs 1!

#### How do we combine those simple formulae?

output

|                                           | р | q | r |

|-------------------------------------------|---|---|---|

| $(\sim p \land \sim q \land \sim r) \lor$ | 0 | 0 | 0 |

|                                           | 0 | 0 | 1 |

| $(\sim p \land q \land r) \lor$           | 0 | 1 | 0 |

|                                           | 0 | 1 | 1 |

|                                           | 1 | 0 | 0 |

| $(p \land \sim q \land \sim r) \lor$      | 1 | 0 | 1 |

|                                           | 1 | 1 | 0 |

| $(p \land q \land r)$                     | 1 | 1 | 1 |

| $(P \land Y \land Y)$                     |   |   |   |

- Outputs 1 if and only if the truth table outputs 1!

- We want to do this in hardware!

#### Logical gates

- The smallest pieces of hardware that we will examine are called *logical gates.*

- Most gates for this course will take **bits** as inputs and will emit one **bit** as output. (Not all gates have this property)

• Those gates can connect to each other in various different ways in order to create more complex circuits

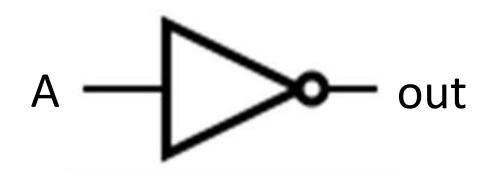

#### Our first gate

| A | out |

|---|-----|

| 0 | 1   |

| 1 | 0   |

- This gate is known as the **inverter**.

- It corresponds **exactly** to the negation operation in propositional logic!

- Where 1, set True.

- Where 0, set False

#### Our second gate

| p | q | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

• Corresponds to:

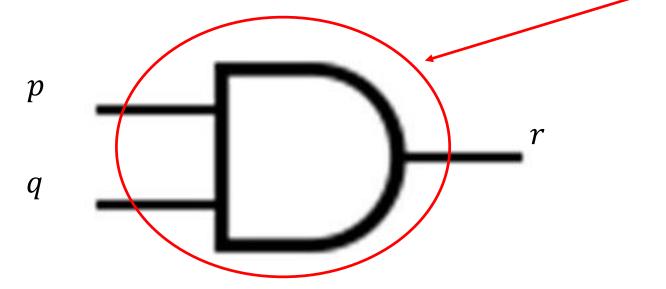

#### Our second gate (AND gate)

| p | q | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

• Corresponds to:

#### Our second gate (AND gate)

| р | q | r |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

|   |   |   |

• Corresponds to:

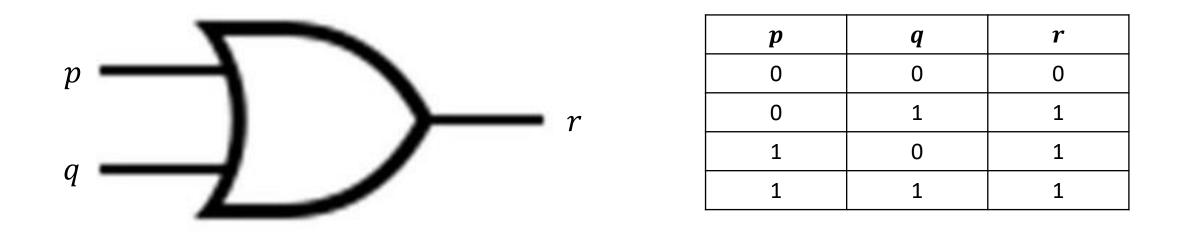

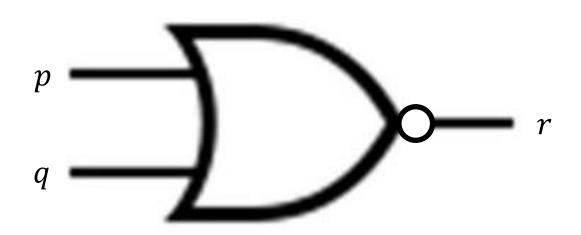

#### Our third gate (OR gate)

• Corresponds to logical disjunction (OR)

#### Our fourth and fifth gate (NAND and NOR gate)

| p | q | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| p | q | r |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

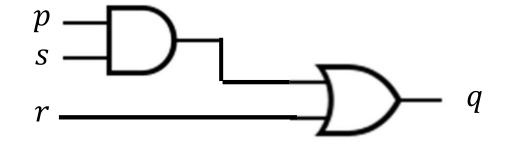

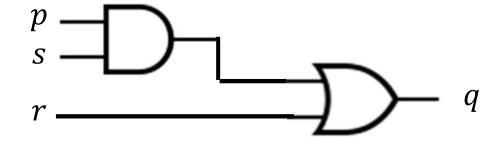

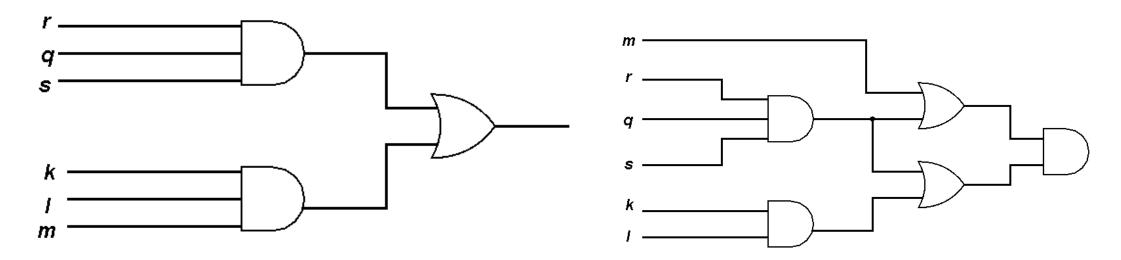

• Which boolean function does this circuit correspond to?

• Which boolean function does this circuit correspond to?

$(p \land s) \lor r$

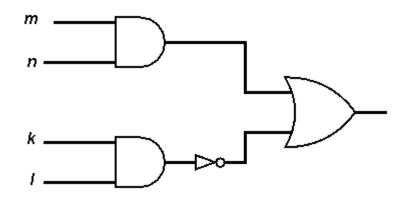

• And this?

• And this?

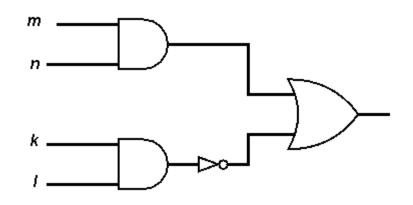

$(m \land n) \lor (\sim (k \land l))$

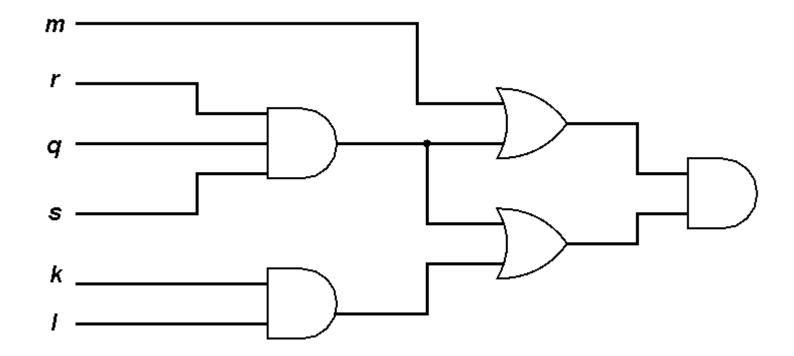

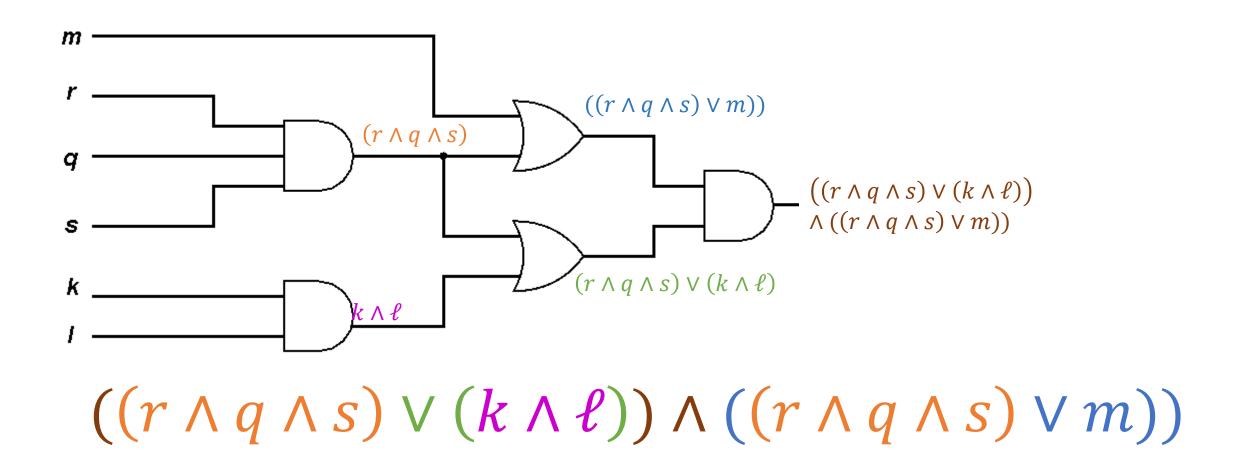

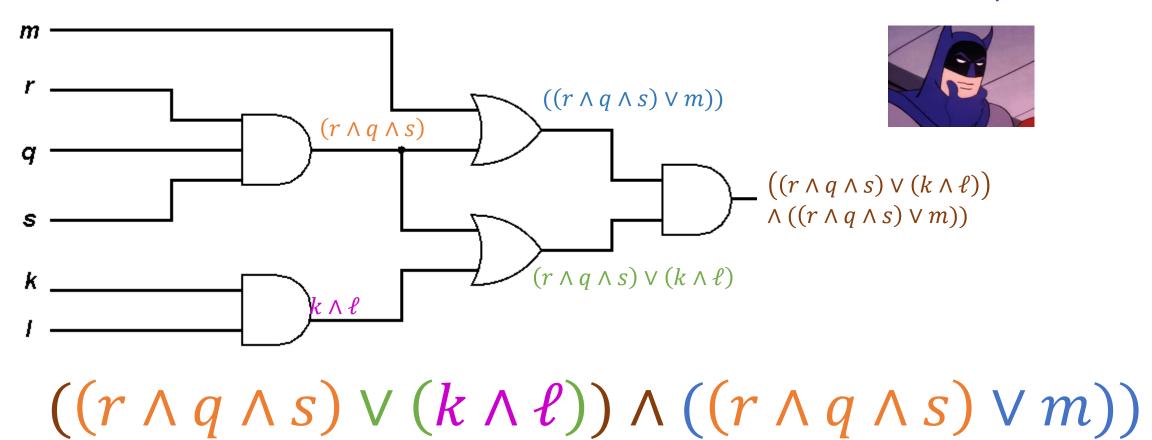

#### And this?

#### And this?

#### And this?

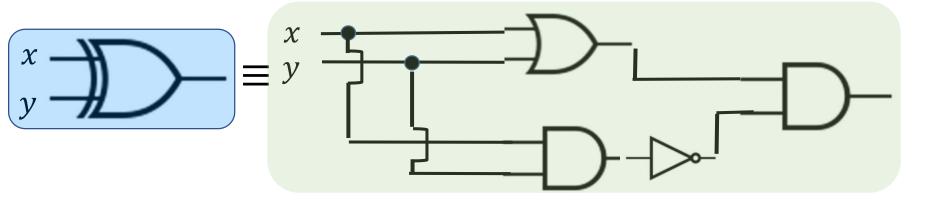

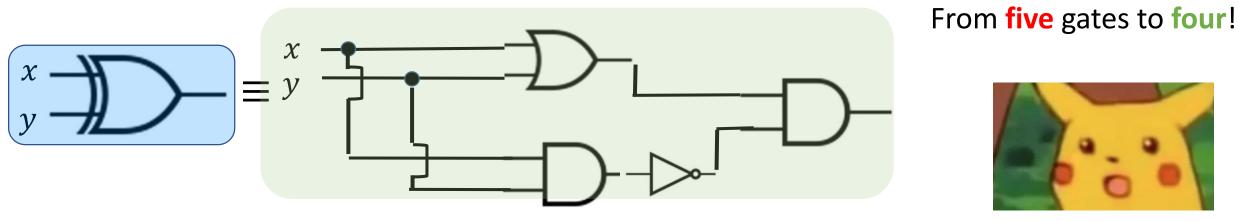

### Can we make this circuit *cheaper*?

#### Simplifying the circuit...

$((r \land q \land s) \lor (k \land \ell)) \land ((r \land q \land s) \lor m)) \equiv (r \land q \land s) \lor ((k \land \ell) \land m)$

New circuit: Three gates

**Old circuit: Five gates**

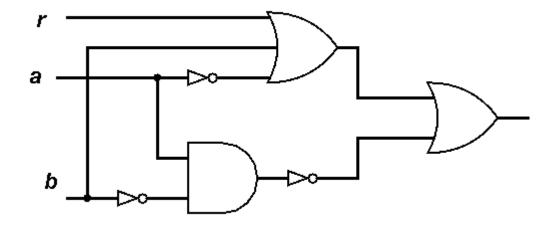

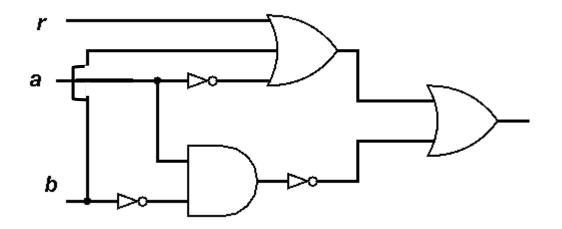

1. Which logical expression is computed by the following circuit?

- 1. Which logical expression is computed by the following circuit?

- 2. *Simplify* the circuit as much as possible!

#### Coming back to our original formula...

$(\sim p \land \sim q \land \sim r) \lor (\sim p \land q \land r) \lor (p \land \sim q \land \sim r) \lor (p \land q \land r)$

#### Coming back to our original formula...

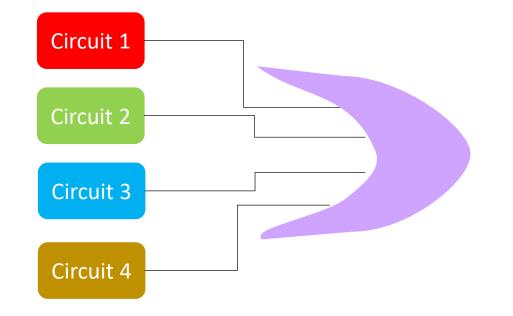

$(\sim p \land \sim q \land \sim r) \lor (\sim p \land q \land r) \lor (p \land \sim q \land \sim r) \lor (p \land q \land r)$

• For each small formula we have a circuit, and we will combine with a 4-input OR gate!

#### Coming back to our original formula...

$(\sim p \land \sim q \land \sim r) \lor (\sim p \land q \land r) \lor (p \land \sim q \land \sim r) \lor (p \land q \land r)$

• For each small formula we have a circuit, and we will combine with a 4-input OR gate!

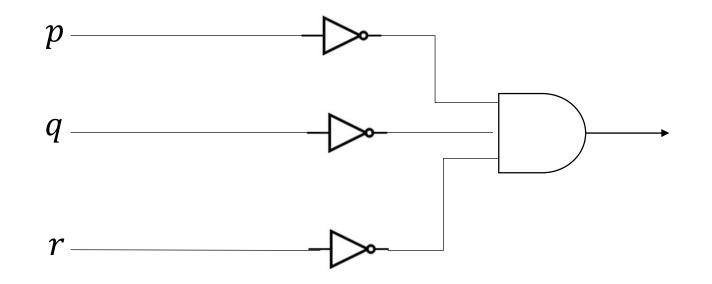

#### Circuit 1

#### $(\sim p \land \sim q \land \sim r)$

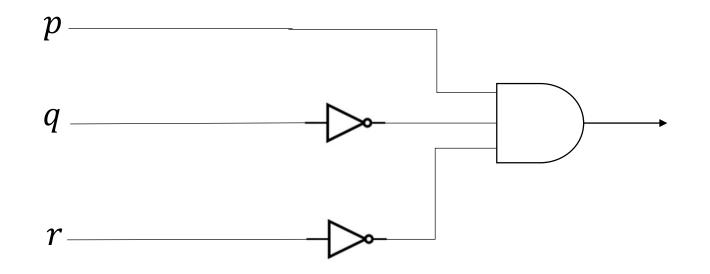

#### Circuit 3 $(p \land \sim q \land \sim r)$

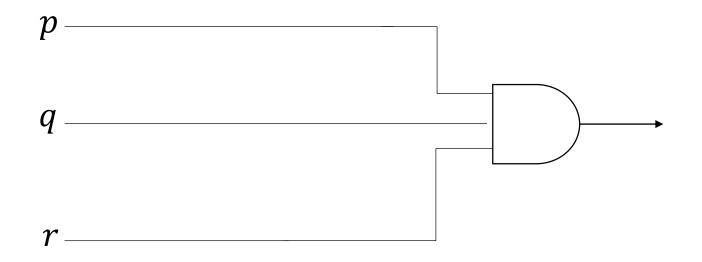

### Circuit 4 $(p \land q \land r)$

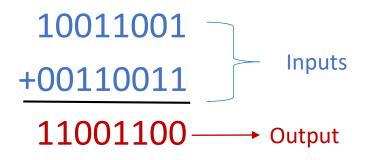

#### **Building Adder Circuits**

- We want to build circuits that add arbitrarily large binary numbers.

- E.g

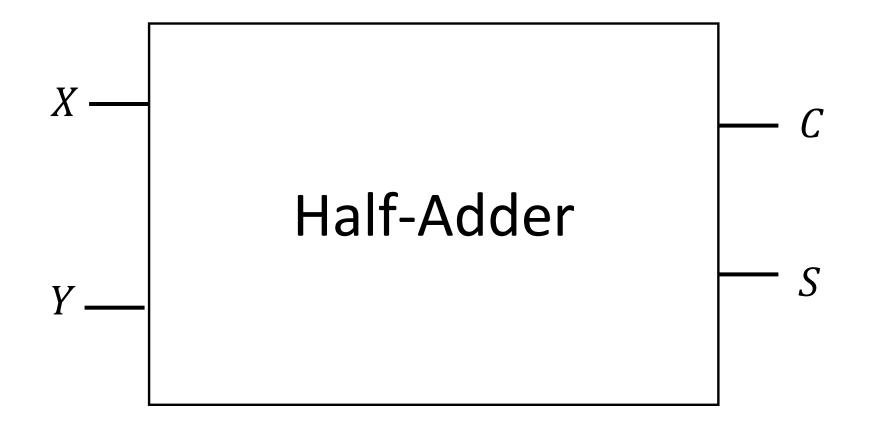

#### Half-Adder

• A half-adder is a circuit that adds two bits together!

$$\frac{X}{Y}$$

- (Remember: *C* is the carry bit.)

- Let's try to build a circuit that computes both S and C!

| X | Y | S | С |

|---|---|---|---|

| 0 | 0 | ? | ? |

| 0 | 1 | ? | ? |

| 1 | 0 | ? | ? |

| 1 | 1 | ? | ? |

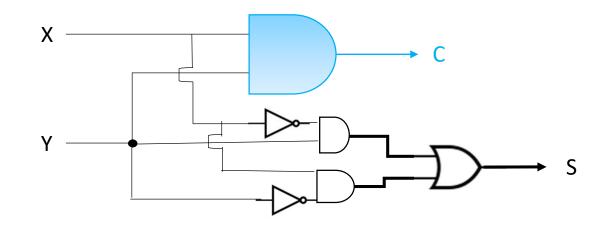

| X | Y | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| X | Y | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| X | Y | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

• First, let's convince ourselves that

• First, let's convince ourselves that

• First, let's convince ourselves that

• First, let's convince ourselves that

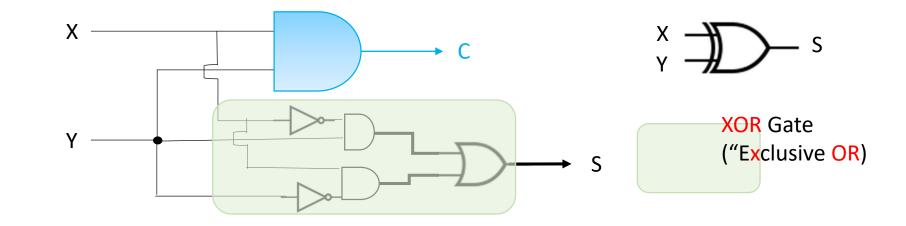

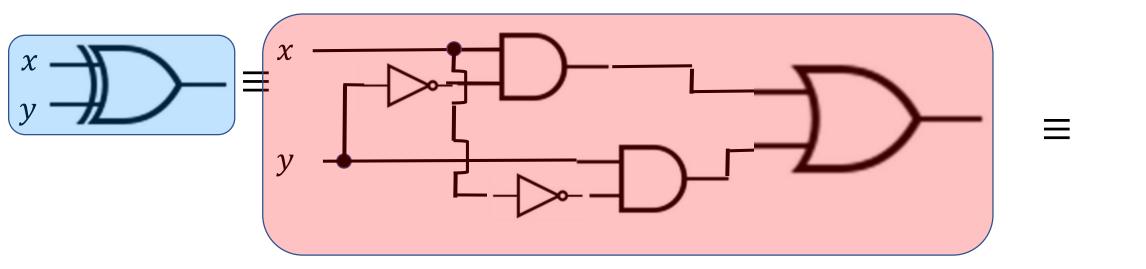

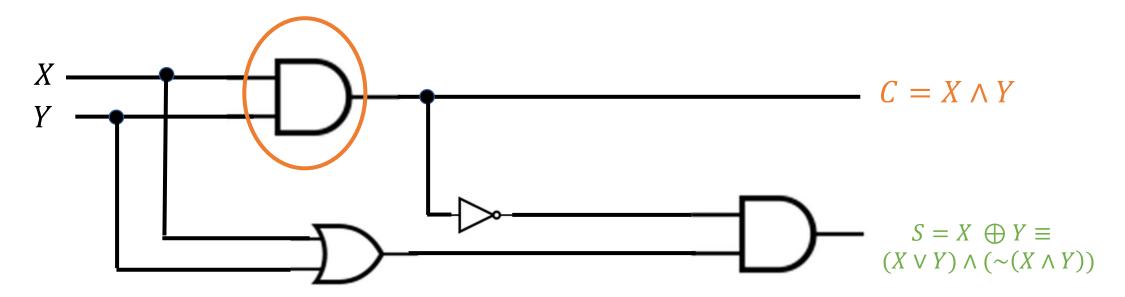

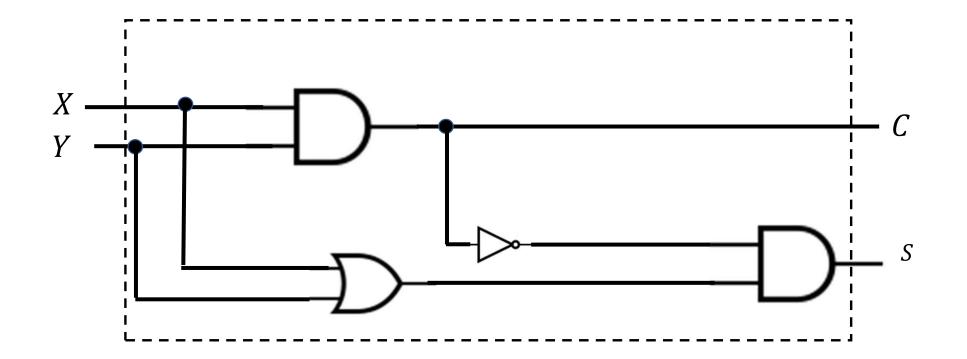

#### Optimizing Half Adder

- We can now optimize the Half Adder.

- We won't just use simplified XOR, but also leverage simplified XOR to <u>re-use</u> the AND gate used to compute the carry bit *C*!

#### Half Adder Abstraction

4 gates, instead of 6 for the previous one!

#### Half Adder Abstraction

#### Full-Adder

• Now, let's consider the complete case, where we want to build a circuit that computes the sum of two 2-digit binary numbers:

P Q +<u>W X</u> C S<sub>1</sub> S<sub>2</sub>

• To do this, we also need the ability to add 3 digits, because:

$\frac{C_1}{P Q}$  + W X  $C S_1 S_2$

#### Full-Adder

• Now, let's consider the complete case, where we want to build a circuit that computes the sum of two 2-digit binary numbers:

P Q +<u>W X</u> C S<sub>1</sub> S<sub>2</sub>

• To do this, we also need the ability to add 3 digits, because:

Ρ

$C S_1 S_2$

We will call a circuit that adds 3 bits a full adder

#### We could do the truth table....

PQ

+<u>WX</u>

|   |   |   |   |   |                | <mark>C S1 S2</mark> |

|---|---|---|---|---|----------------|----------------------|

| Р | Q | W | X | С | S <sub>1</sub> | S <sub>2</sub>       |

| 0 | 0 | 0 | 0 |   |                |                      |

| 0 | 0 | 0 | 1 |   |                |                      |

| 0 | 0 | 1 | 0 |   |                |                      |

| 0 | 0 | 1 | 1 |   |                |                      |

| 0 | 1 | 0 | 0 |   |                |                      |

| 0 | 1 | 0 | 1 |   |                |                      |

| 0 | 1 | 1 | 0 |   |                |                      |

| 0 | 1 | 1 | 1 |   |                |                      |

| 1 | 0 | 0 | 0 |   |                |                      |

| 1 | 0 | 0 | 1 |   |                |                      |

| 1 | 0 | 1 | 0 |   |                |                      |

| 1 | 0 | 1 | 1 |   |                |                      |

| 1 | 1 | 0 | 0 |   |                |                      |

| 1 | 1 | 0 | 1 |   |                |                      |

| 1 | 1 | 1 | 0 |   |                |                      |

| 1 | 1 | 1 | 1 |   |                |                      |

#### We could do the truth table....

PQ

+<u>WX</u>

|   |   |   |   |  |                     |                | <mark>C S1 S2</mark> |  |  |

|---|---|---|---|--|---------------------|----------------|----------------------|--|--|

| Р | Q | W | X |  | С                   | S <sub>1</sub> | S <sub>2</sub>       |  |  |

| 0 | 0 | 0 | 0 |  |                     |                |                      |  |  |

| 0 | 0 | 0 | 1 |  |                     |                |                      |  |  |

| 0 | 0 | 1 | 0 |  |                     |                |                      |  |  |

| 0 | 0 | 1 | 1 |  |                     |                |                      |  |  |

| 0 | 1 | 0 | 0 |  |                     |                |                      |  |  |

| 0 | 1 | 0 | 1 |  |                     | But it's time  |                      |  |  |

| 0 | 1 | 1 | 0 |  |                     |                |                      |  |  |

| 0 | 1 | 1 | 1 |  | consuming and we    |                |                      |  |  |

| 1 | 0 | 0 | 0 |  |                     |                |                      |  |  |

| 1 | 0 | 0 | 1 |  | are all busy people |                |                      |  |  |

| 1 | 0 | 1 | 0 |  |                     |                |                      |  |  |

| 1 | 0 | 1 | 1 |  |                     |                |                      |  |  |

| 1 | 1 | 0 | 0 |  |                     |                |                      |  |  |

| 1 | 1 | 0 | 1 |  |                     |                |                      |  |  |

| 1 | 1 | 1 | 0 |  |                     |                |                      |  |  |

| 1 | 1 | 1 | 1 |  |                     |                |                      |  |  |

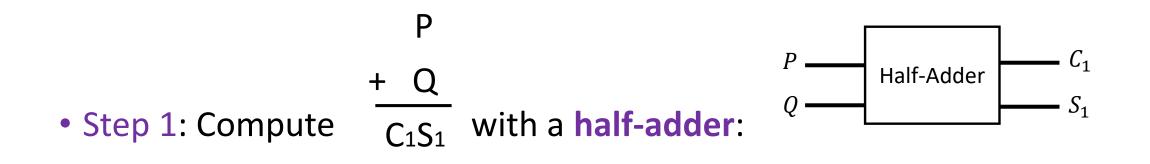

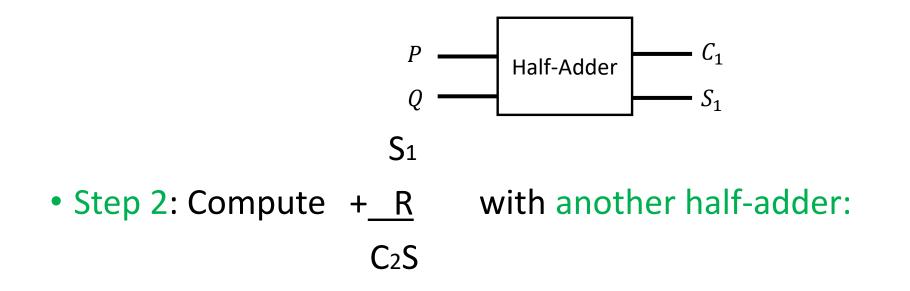

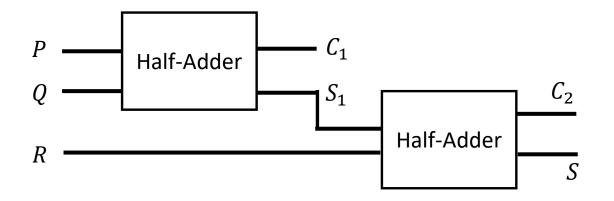

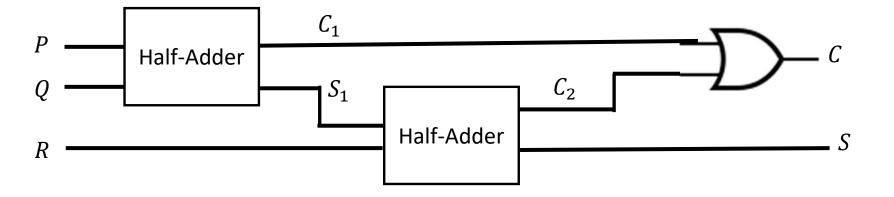

#### Constructing a Full-Adder in another way

We need to build a circuit that computes the sum of 3 digits, e.g P + Q + R

#### Constructing a Full Adder

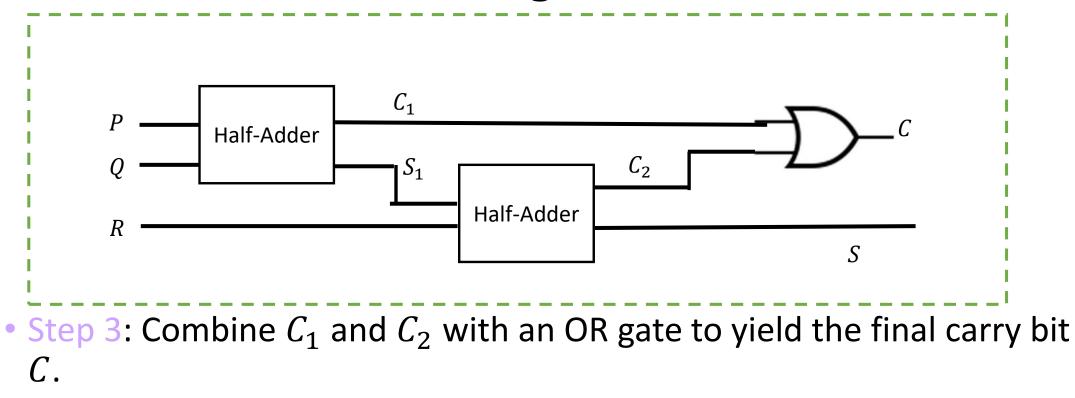

#### Constructing a full-adder

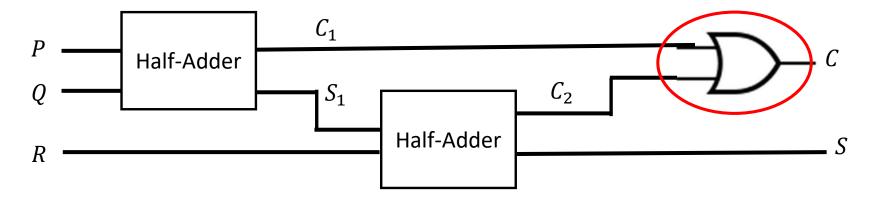

• Step 3: Combine  $C_1$  and  $C_2$  with an OR gate to yield the final carry bit C.

#### Constructing a full-adder

- Step 3: Combine  $C_1$  and  $C_2$  with an OR gate to yield the final carry bit C.

- Why did we choose an OR gate to combine the "intermediate" carries C<sub>1</sub> and C<sub>2</sub>?

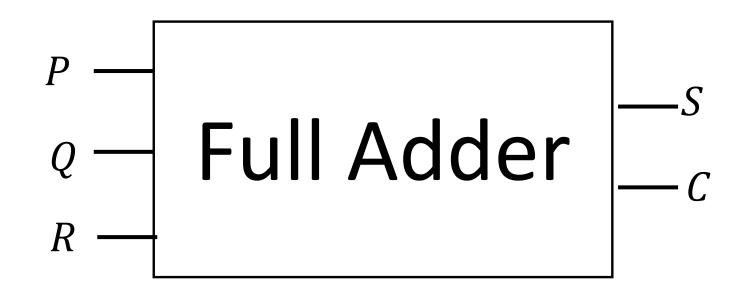

#### Constructing a full-adder

## Abstraction time!

#### Full Adder Black Box

• 3 inputs, 2 outputs

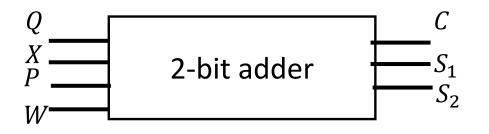

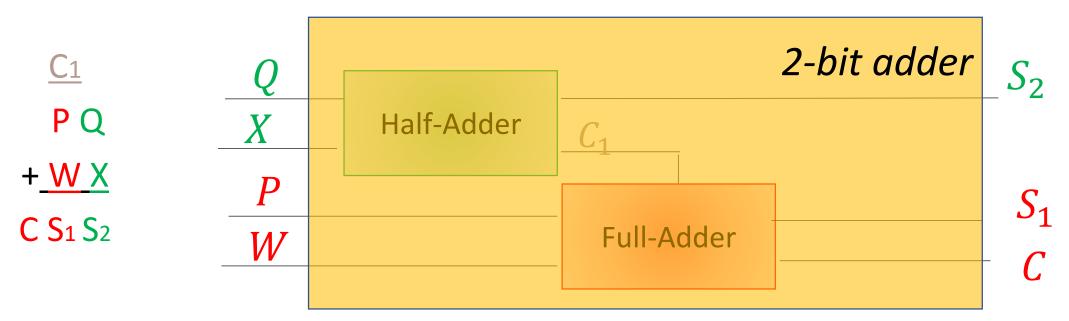

#### 2-bit adder

• However, **we still have not solved our original problem**, which is to construct a circuit that adds 2-bit numbers!

P Q +<u>W X</u> C S<sub>1</sub> S<sub>2</sub>

• So, we need a circuit that takes 4 inputs and emits 3 outputs:

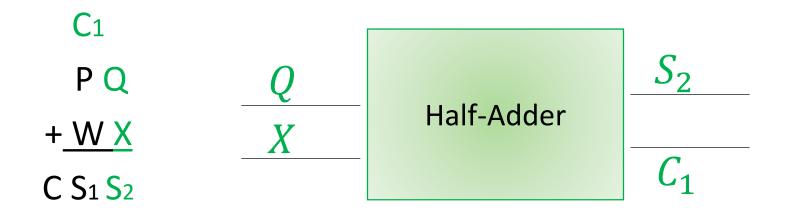

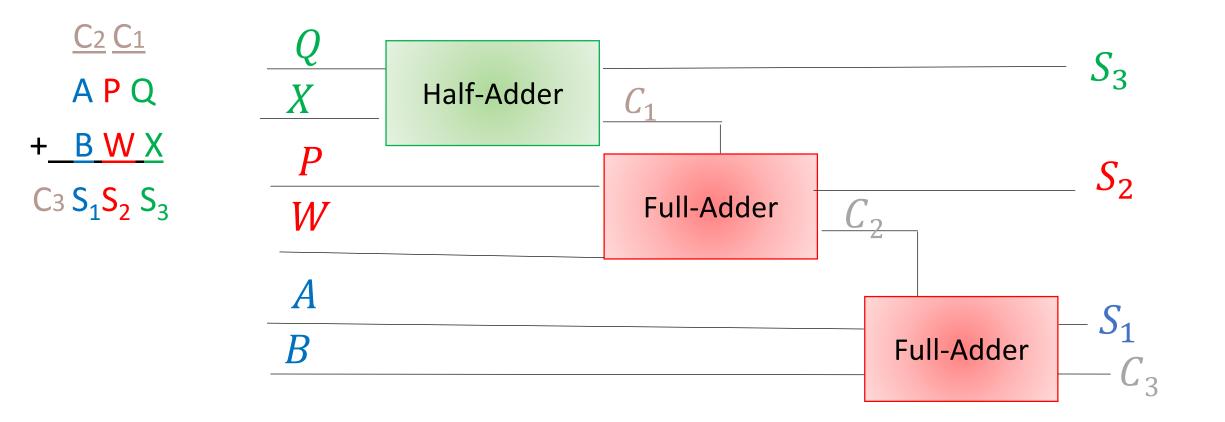

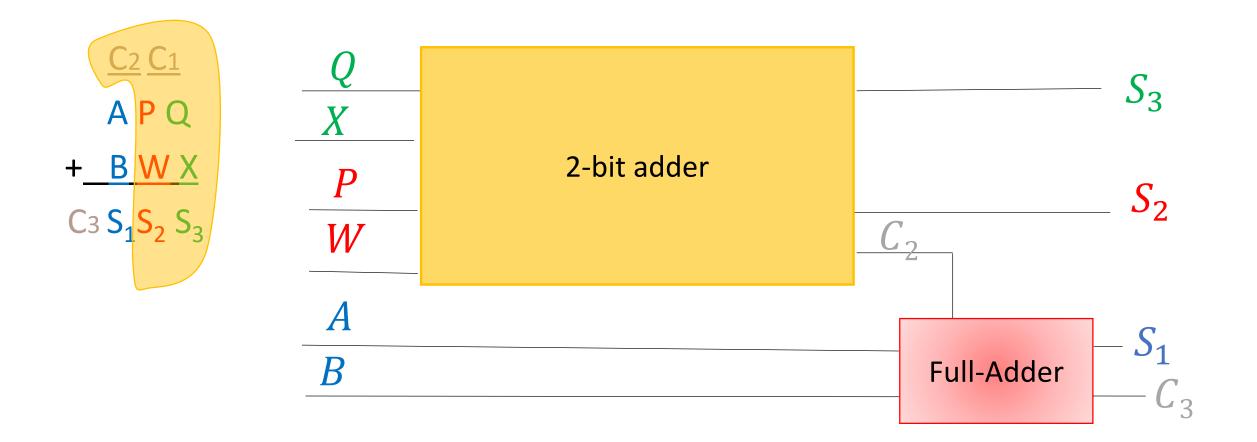

#### Constructing a 2-bit adder

• Step 1: Take care of the right-most column with a half-adder:

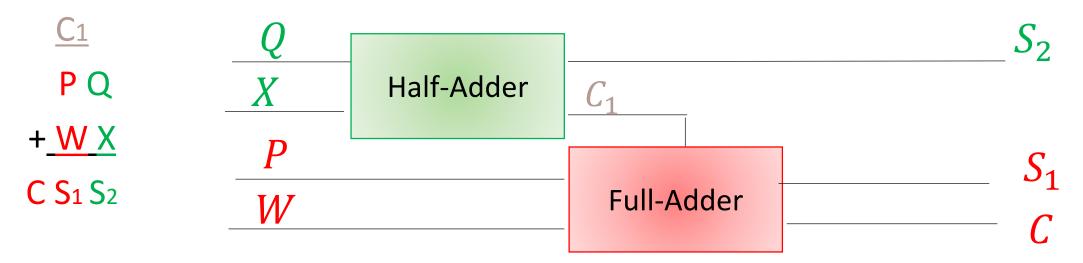

#### Constructing a 2-bit adder

• Step 1: Take care of the right-most column with a half-adder:

• Step 2 (and final): Connect Half-Adder and new inputs to Full-adder appropriately to produce final circuit.

#### Constructing a 2-bit adder

• Step 1: Take care of the right-most column with a half-adder:

Step 2 (and final): Connect Half-Adder and new inputs to Full-adder appropriately to produce final circuit.

#### Constructing a 3-bit adder (messy)

#### Constructing a 3-bit adder (neat)

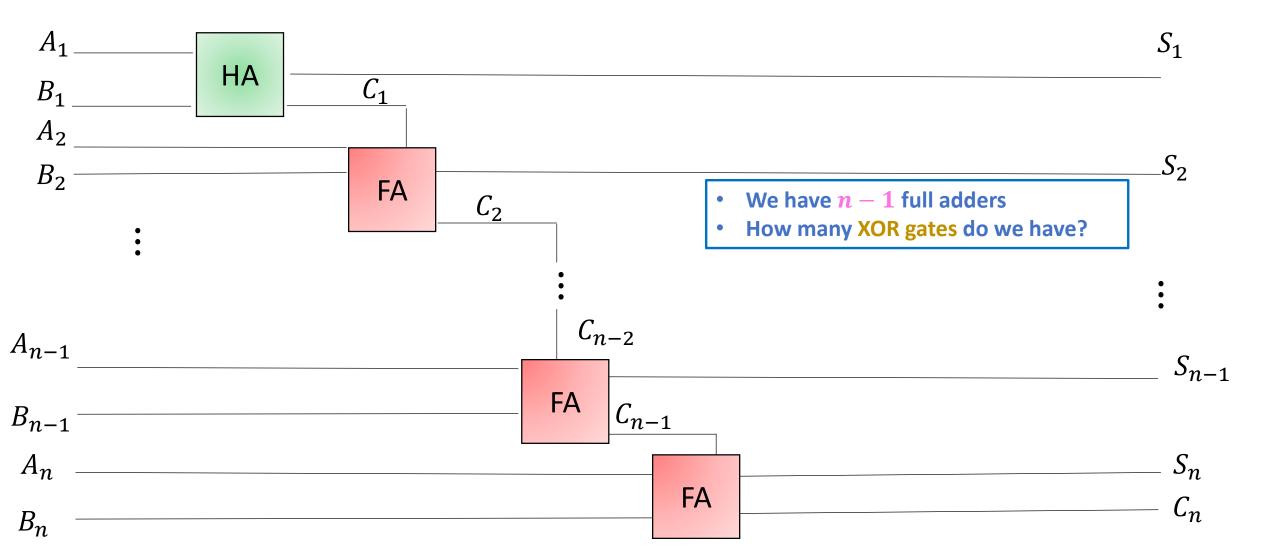

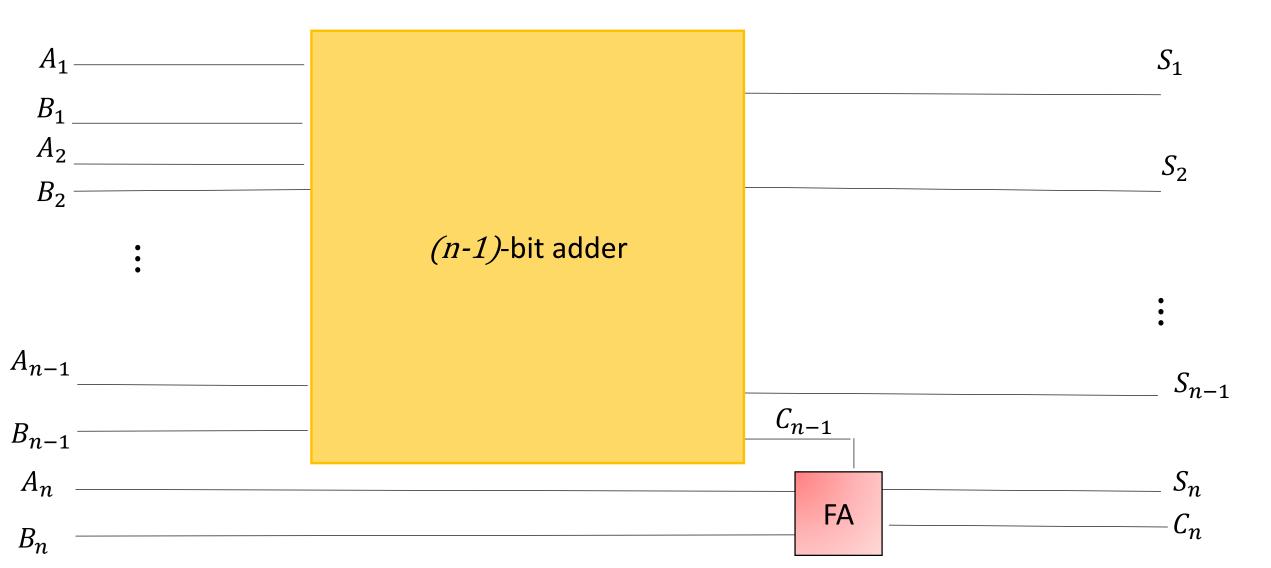

#### Constructing an n-bit adder (messy)

#### Constructing an n-bit adder (neat)

#### Other numeric functions

- Addition (have done)

- Multiplication

- Division

- Primality test (test whether a number is prime)

- There are circuits for all of these!

- Computers actually work this way at the base level: they consist of gates.

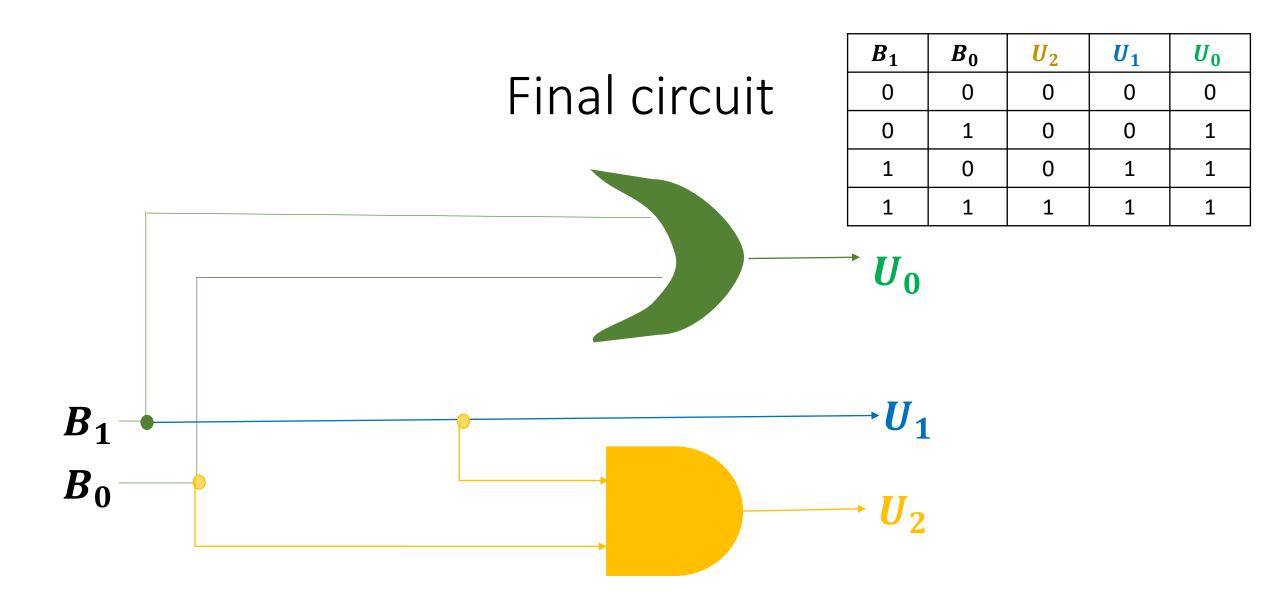

#### Fun exercise

- Input: number in **binary**

- Output: ??? (you will tell me later)

| <b>B</b> <sub>1</sub> | B <sub>0</sub> | <i>U</i> <sub>2</sub> | <i>U</i> <sub>1</sub> | U <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|----------------|

| 0                     | 0              | 0                     | 0                     | 0              |

| 0                     | 1              | 0                     | 0                     | 1              |

| 1                     | 0              | 0                     | 1                     | 1              |

| 1                     | 1              | 1                     | 1                     | 1              |

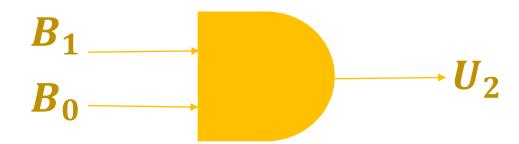

#### First micro-circuit

| <b>B</b> <sub>1</sub> | B <sub>0</sub> | <i>U</i> <sub>2</sub> | <i>U</i> <sub>1</sub> | U <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|----------------|

| 0                     | 0              | 0                     | 0                     | 0              |

| 0                     | 1              | 0                     | 0                     | 1              |

| 1                     | 0              | 0                     | 1                     | 1              |

| 1                     | 1              | 1                     | 1                     | 1              |

$\boldsymbol{U}_2 = \boldsymbol{B}_1 \wedge \boldsymbol{B}_0$

#### Second micro-circuit

| <b>B</b> <sub>1</sub> | B <sub>0</sub> | <i>U</i> <sub>2</sub> | <i>U</i> <sub>1</sub> | U <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|----------------|

| 0                     | 0              | 0                     | 0                     | 0              |

| 0                     | 1              | 0                     | 0                     | 1              |

| 1                     | 0              | 0                     | 1                     | 1              |

| 1                     | 1              | 1                     | 1                     | 1              |

$\boldsymbol{U}_1 = (\boldsymbol{B}_1 \wedge \boldsymbol{\sim} \boldsymbol{B}_0) \vee (\boldsymbol{B}_1 \wedge \boldsymbol{B}_0)$

#### Second micro-circuit

| <b>B</b> <sub>1</sub> | B <sub>0</sub> | <i>U</i> <sub>2</sub> | <i>U</i> <sub>1</sub> | U <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|----------------|

| 0                     | 0              | 0                     | 0                     | 0              |

| 0                     | 1              | 0                     | 0                     | 1              |

| 1                     | 0              | 0                     |                       | 1              |

|                       | 1              | 1                     |                       | 1              |

|                       |                |                       |                       |                |

$\boldsymbol{U}_1 = (\boldsymbol{B}_1 \wedge \boldsymbol{\sim} \boldsymbol{B}_0) \vee (\boldsymbol{B}_1 \wedge \boldsymbol{B}_0) = \boldsymbol{B}_1$

(from distributive law of conjunction over disjunction!)

$B_1 \longrightarrow U_1$

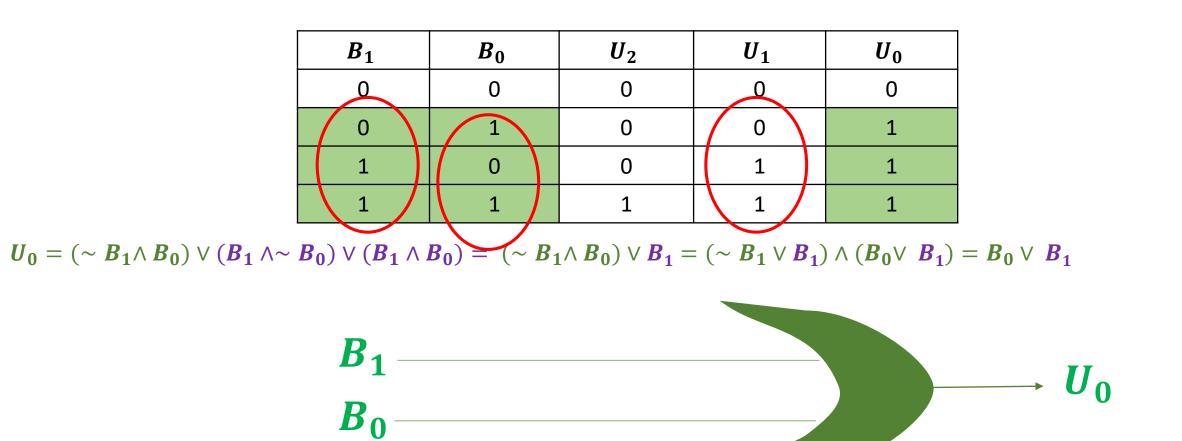

#### Third micro-circuit

| <b>B</b> <sub>1</sub> | B <sub>0</sub> | <i>U</i> <sub>2</sub> | <i>U</i> <sub>1</sub> | U <sub>0</sub> |

|-----------------------|----------------|-----------------------|-----------------------|----------------|

| 0                     | 0              | 0                     | 0                     | 0              |

| 0                     | 1              | 0                     | 0                     | 1              |

| 1                     | 0              | 0                     | 1                     | 1              |

| 1                     | 1              | 1                     | 1                     | 1              |

$U_0 = (\sim B_1 \land B_0) \lor (B_1 \land \sim B_0) \lor (B_1 \land B_0)$

#### Third micro-circuit

# STOP RECORDING