RISC-Q: A generator for real-time quantum control system-on-chip (SoCs) compatible with RISC-V

|

RISC-Q is an open-source (Github) generator (i.e., design automation tool) for Quantum Control System-on-Chip (QCSoC) designs, featuring a programming interface compatible with the RISC-V ecosystem. RISC-Q enables efficient automation of highly parameterized and modular QCSoC architectures, supporting agile and iterative development to explore the hardware–software co-design space and accelerate rapid prototyping and customization. |

RISC-Q Vision

The transformative advances of quantum computing will only be realized when systems can scale reliably and efficiently. In the past decade, quantum hardware has seen rapid progress across multiple implementation technologies. Although today’s quantum computers have not yet reached practical utility, their rapid scaling is already intensifying demands on the quantum control stack. Quantum control systems, originally designed for proof-of-concept demonstrations in meticulously controlled lab settings, must now evolve to meet industrial demands—delivering unprecedented levels of precision, timing accuracy, and scalable operation. This transformation positions them not merely as supporting hardware, but as the critical infrastructure enabling practical, high performance quantum computing.

We believe that efficient customization and prototyping of QCSoCs built upon an open-source ecosystem will be crucial for the community to develop a truly scalable quantum control system. RISC-Q is designed to fulfill this vision with inspiration from the open-source ecosystem for building classical hardware accelarators based on RISC-V. This complements the existing specific open source QCSoC systems (i.e., QubiC, QICK, Artiq) as well as closed-source commericial systems from, e.g., Quantum Machines, Qblox, Zurich Instrument.

RISC-V Compatibility

Support Quantum Computing/Sensing/Network across technologies (e.g., super-conducting, trapped-ion, neutral atoms, spin qubits)

Fast Customization and Prototyping on FPGA and ASIC

Scalable Multi-chip/board Synchronization and Communication

Built-in Interoperability and Support for an Open-Source Community

Highly-efficient Reference Implementation for the Core Control and Hardware Acceleration Kernels (e.g., QEC)

RISC-Q Overview

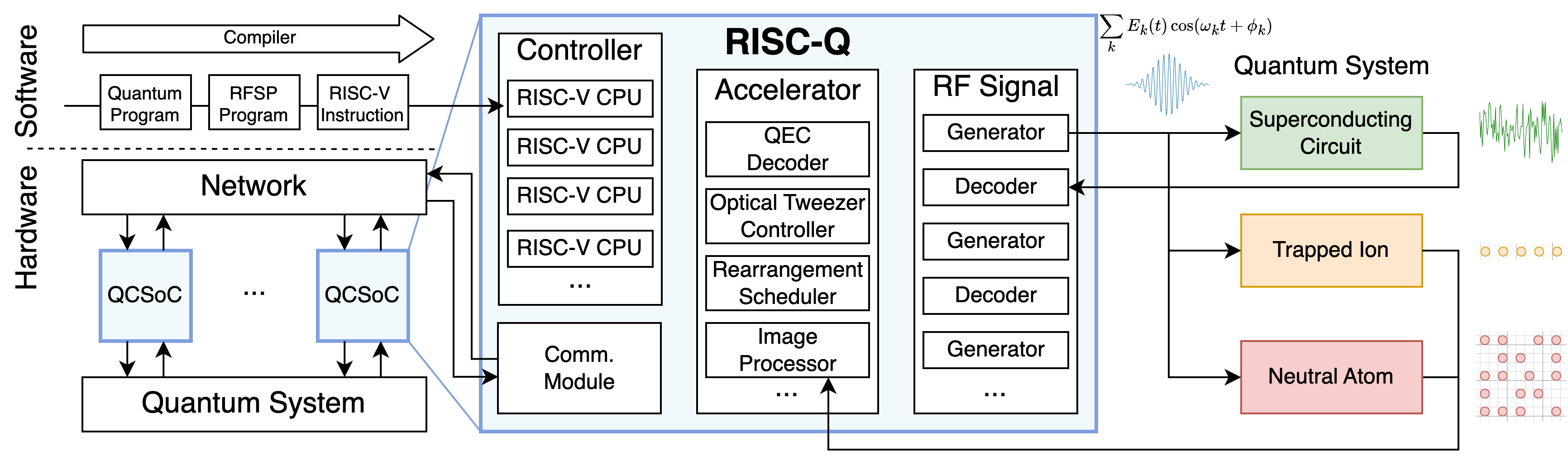

The following figure illustrates the RISC-Q modeling of a typical quantum control system architecture. The system components are categorized based on their functions, including RF signal processors, controllers, custom accelerators, and communication modules, illustrated as follows.

|

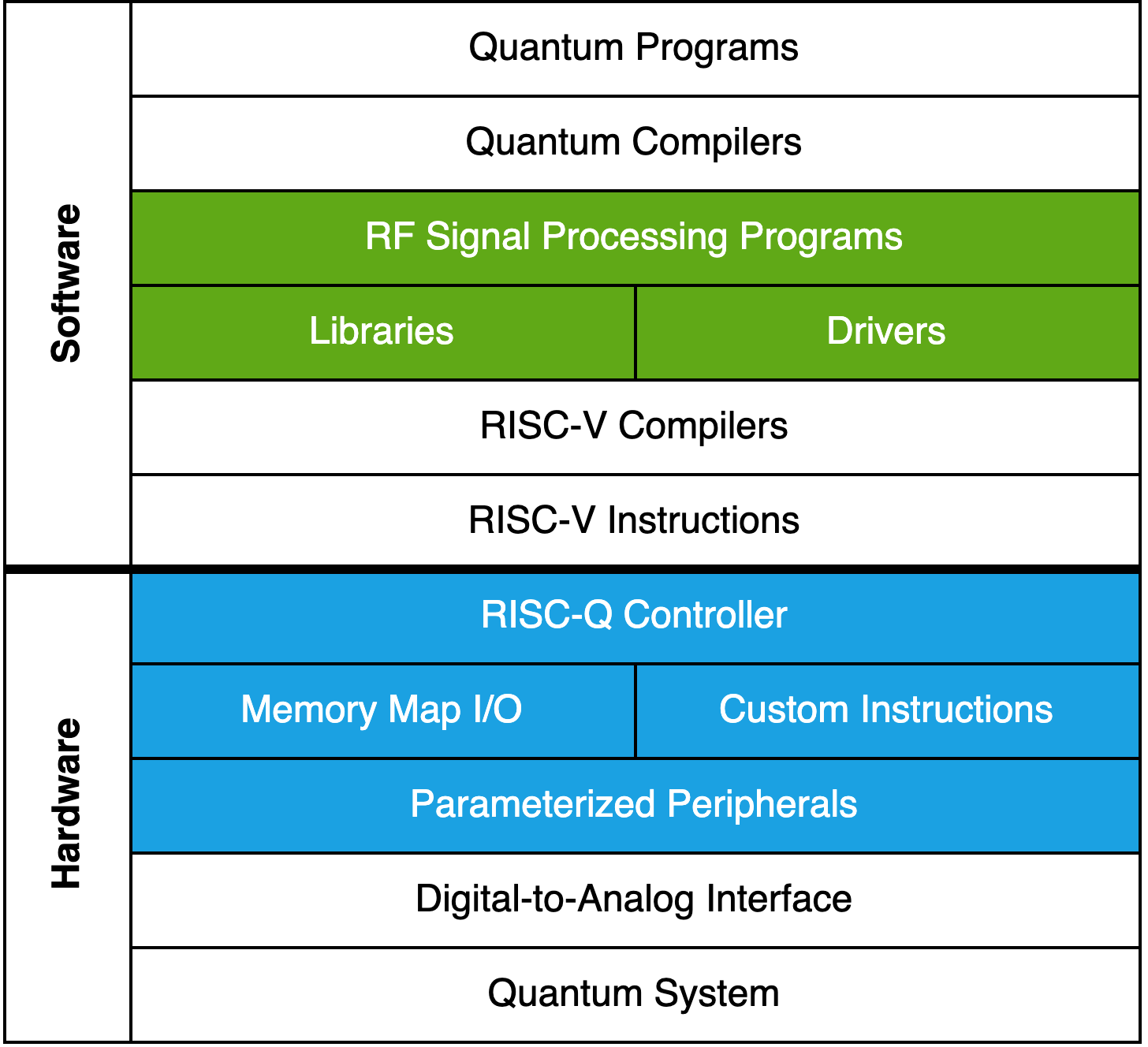

RISC-Q also features the following programming interface that allows one to write any pulse-level program in RISC-V compatible languages (e.g., C, Rust) that will run fully on chip. As a result, one can directly develop on-chip calibration/control/sensing/learning protocols with feedbacks in existing high-level programming languages (e.g., a library in C is provided). A debugging and testing tool for the development of on-chip protocols is under development.

|

A comparison with QICK and QubiC is summarized in the following table:

| QICK | QubiC | RISC-Q | |

| Controller FMax / MHz | 384 | 500 | 500 |

| Output Lines / Board | 13 | 16 | 16 |

| Output Tones / Board | 20 | 16 | 28 |

| Qubits / Board | 6 | 8 | 14 |

| Feedback Latency / ns | 184 | 150 (a) | 144 (a) |

| Network Latency / ns | N/A | 450 (b) | 156 (b) |

| Jitter / ps | N/A | 1.8 (c) | 1.43 (c) |

| QEC Integration | No | No | Yes |

a Feedback latency is evaluated in the fast reset task.

b Network latency is evaluated for the one-way communication latency between two directly connected QCSOCs.

c Root-Mean-Square (RMS) jitter integrating from 10 Hz to 100 MHz at 6.5 GHz.

More details can be found at 2505.14902.

Ongoing Projects based on RISC-Q

Migration of QubiC and QICK to RISC-Q-based development for future releases. In collaboration with both Qubic and QICK teams.

A Scalable Open-Source QEC System with Sub-Microsecond Decoding-Feedback Latency.

A Scalable, High-throughput, and Resource Efficient Real-time Hardware Decoder for Quantum LDPC codes.

More TBA.

Tutorials & Talks

RISC-Q: A Brief Introduction (up to frequent updates)

May 2025. 45 min slides

Mini-Lecture Series on System-Level Design for Quantum Real-time Control and Error Correction

Lecture 1: Real-Time Requirements for Controlling Quantum Systems (slides)

Lecture 2: Quantum Error Correction–Related System Design (slides)

Lecture 3: RISC-Q as a Generator for Quantum Control SoCs (slides)

Lecture 4: Case Study: RISC-Q–Based Quantum Error Correction System (slides)

Lecture 5: Case Study: RISC-Q–Enabled Hardware Acceleration Modules (slides)

Citation

If you use RISC-Q in your work, please cite our paper:

RISC-Q: A Generator for Real-Time Quantum Control System-on-Chips Compatible with RISC-V

Junyi Liu, Yi Lee, Haowei Deng, Connor Clayton, Gengzhi Yang, Xiaodi Wu

ArXiv: 2505.14902, Github: RISC-Q

@misc{liu2025riscqgeneratorrealtimequantum,

title={RISC-Q: A Generator for Real-Time Quantum Control System-on-Chips Compatible with RISC-V},

author={Junyi Liu and Yi Lee and Haowei Deng and Connor Clayton and Gengzhi Yang and Xiaodi Wu},

year={2025},

eprint={2505.14902},

archivePrefix={arXiv},

primaryClass={cs.AR},

url={https://arxiv.org/abs/2505.14902},

}

Acknowledgments

We are deeply grateful to David Schuster for introducing open-source quantum control systems, which served as the inspiration for this entire project. We sincerely thank the QubiC team—especially Gang Huang and Yilun Xu—for their invaluable assistance in testing the RISC-Q generated prototype, Will Oliver’s group for generously sharing their control hardware, and the QICK team for their help in understanding their codebase. We are also grateful for the insightful discussions with Hanrui Wang, Margaret Martonosi, Fred Chong, Jens Palsberg, Swamit Tannu, Adam Chlipala, Mark Horowitz, Priyanka Raina, Jason Cong, and Lin Zhong throughout the various stages of RISC-Q’s development, which helped shape its current form.

This project is partially supported by Air Force Office of Scientific Research under award number FA9550-21-1-0209, the U.S. National Science Foundation grant CCF-1942837 (CAREER), CCF-2330974, NQVL-2435244, and a Sloan Research Fellowship